MOSキャパシタ(MOS構造)の動作原理とバンド図

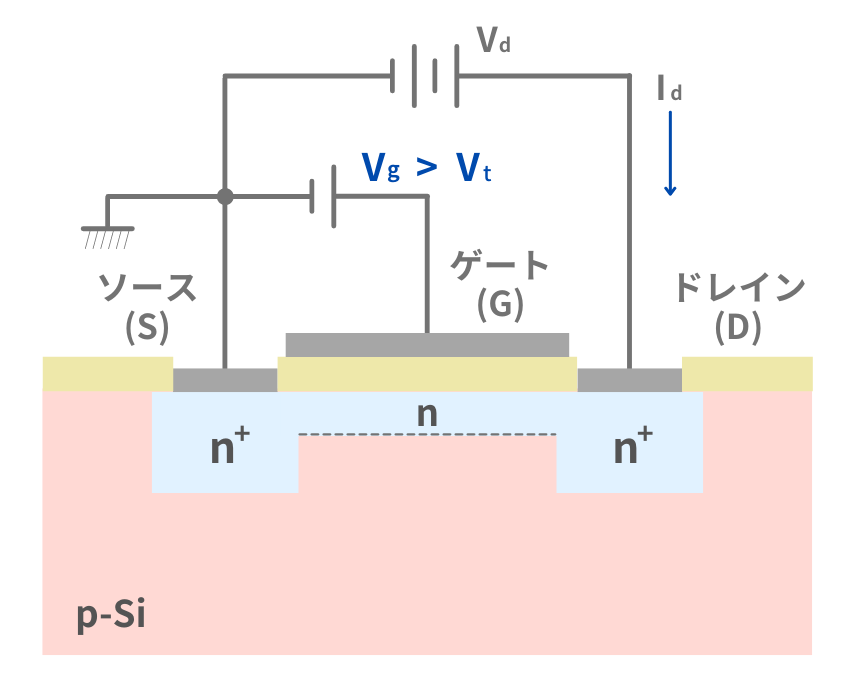

MOSFETの動作原理

MOSFETは、ゲート電圧によって半導体表面のキャリア濃度を制御し、チャネルを形成することで、ソース・ドレイン間の電流のON/OFFを切り替えるデバイスです。

チャネルは表面で形成される反転層であり、この反転層を通じて電子が流れることで電流が制御されます。

なぜ、このように電圧でチャネルができるのかは、バンド図を使うとより論理的に理解できます。

MOSFETの基本構造:MOSキャパシタ

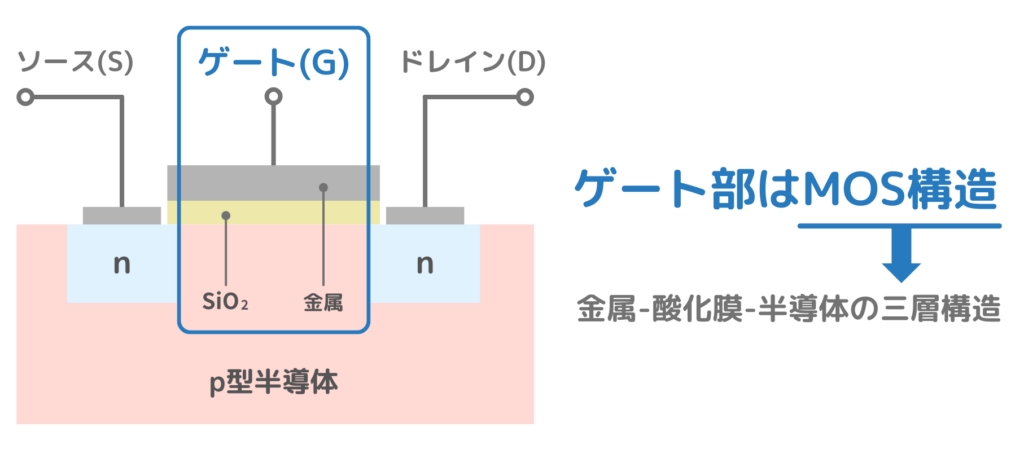

MOSFETゲート部はMOS構造(MOSキャパシタ)で構成されます。

MOS構造とは金属(Metal)・酸化膜(Oxide)・半導体(Semiconductor)の三層構造を指します。

MOSFETにおけるゲート直下はMOS構造であり、チャネル形成(反転層形成)はMOSキャパシタのバンド図を理解することが重要です。

以降、nチャネルMOSFET(金属-酸化膜-p型半導体の三層構造)を例に、MOSキャパシタの動作を理解していきます。

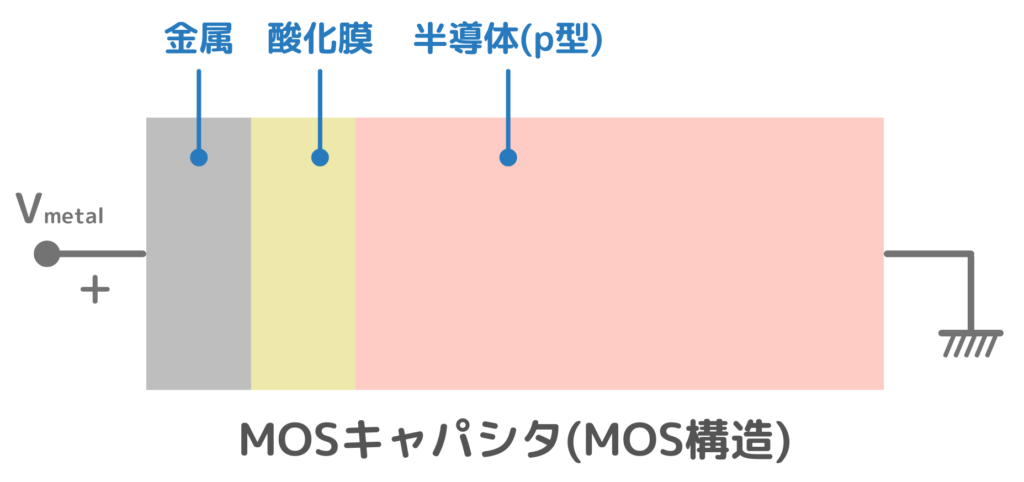

MOSキャパシタの動作原理

MOSキャパシタの金属側(ゲート電極側)に以下の電圧を印加した場合を考えます。

- 負電圧:VG < 0

- 閾値電圧以下の正電圧:0 < VG < Vth

- 閾値電圧以上の正電圧:Vth < VG

閾値電圧Vthとは、反転層が形成し、ソース-ドレイン間が接続され電流が流れる(ON)になる電圧のことです。

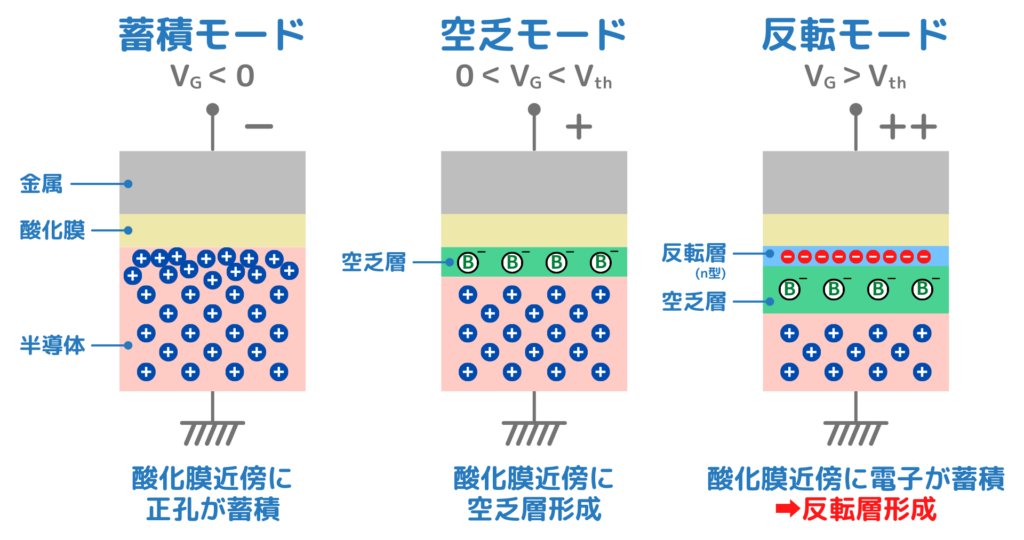

- 蓄積モード:VG < 0

- 空乏モード:0 < VG < Vth

- 反転モード:Vth < VG

p型基板中の多数キャリアである正孔が酸化膜直下の表面に引き寄せられ、表面に正孔が蓄積。nチャネルは形成されず、ソース・ドレイン間には電流は流れない。

正電圧に反発される形で酸化膜直下表面の正孔が押し出され、キャリアの少ない空乏層が形成。表面はまだn型に反転しておらず、ソース・ドレイン間には電流は流れない。

正電圧に引かれる形で酸化膜直下に電子が蓄積。反転層(チャネル)が形成され、ソース・ドレイン間に電流が流れる(ON状態)。

定性的に、MOSキャパシタで反転層が形成される原理を理解できました。

MOS構造(MOSキャパシタ)のバンド図

ここではnチャネルMOSFETを例に、MOSキャパシタのバンド図を理解していきます。

0. バンド図に出てくるエネルギー準位の意味

MOSFETの動作をバンド図で理解するために、まず基本となるエネルギー準位の意味を簡単に整理します。

バンド図の縦軸は電子のエネルギーを表しており、上に行くほど電子のエネルギーが高い状態を意味します。

- EC(伝導帯端)

- EV(価電子帯端)

- Ei(真性準位)

- EF(フェルミ準位)

電子が自由に移動できるエネルギー帯の下端を表しますzECに近いほど、電子は動きやすくなります。

電子が原子に束縛されているエネルギー帯の上端を表します。p型半導体では、この近くにフェルミ準位が位置します。

電子とホールの数が等しくなるエネルギー位置で、半導体がn型かp型かを判断する基準として使われます。

電子が占有される確率が50%となるエネルギー準位です。熱平衡状態では空間的に一定となります。

熱平衡状態ではフェルミ準位EF は空間的に一定でなければなりません。もしフェルミ準位に差があれば、電子は EF が高い側から低い側へ自発的に移動し、最終的に EF は一定になるためです。

そのためバンド図では、EFを基準線として固定し、ゲート電圧によって変化する半導体表面の電位をECやEi の曲がりとして表現します。

バンド図を読む際は、フェルミ準位 EFを動かさずに考え、ECやEiが表面でエネルギー的にどれだけ下がるかを見ることが重要です。

ECがフェルミ準位EFに近づくほど、電子の存在確率は指数関数的に高くなります。さらにゲート電圧を上げて表面の真性準位 Ei がEFを下回ると、表面はn型に反転し、電子が多数キャリアとして集まってチャネルが形成されます。

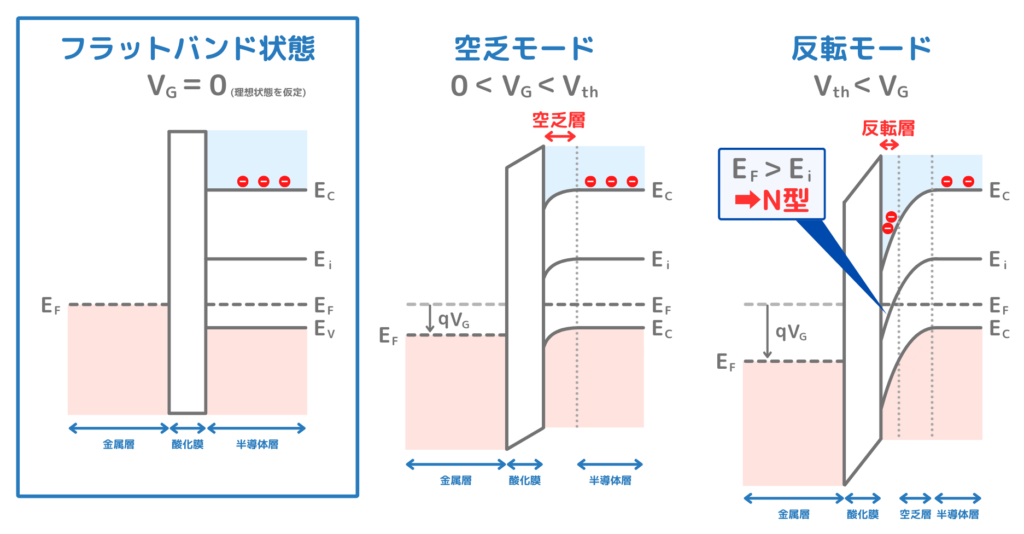

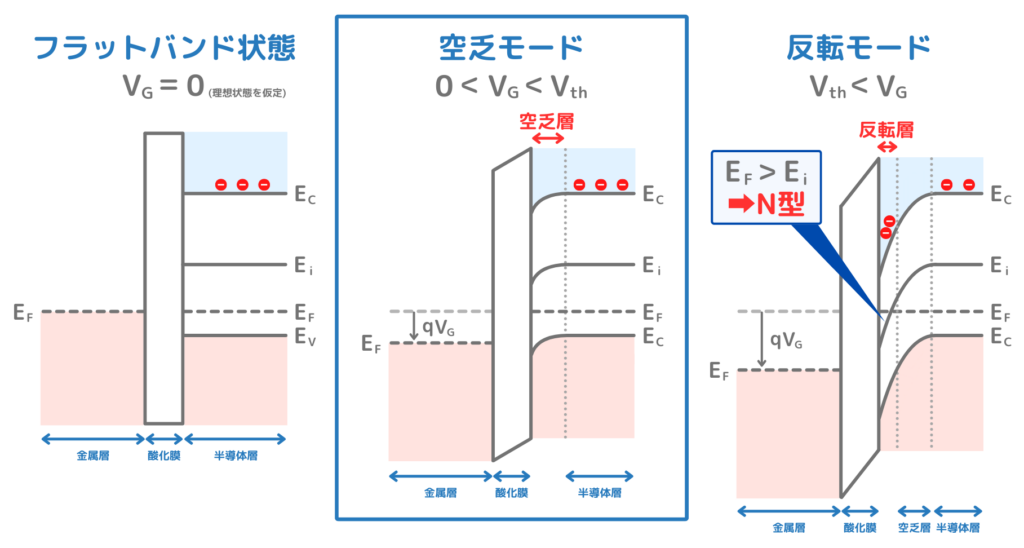

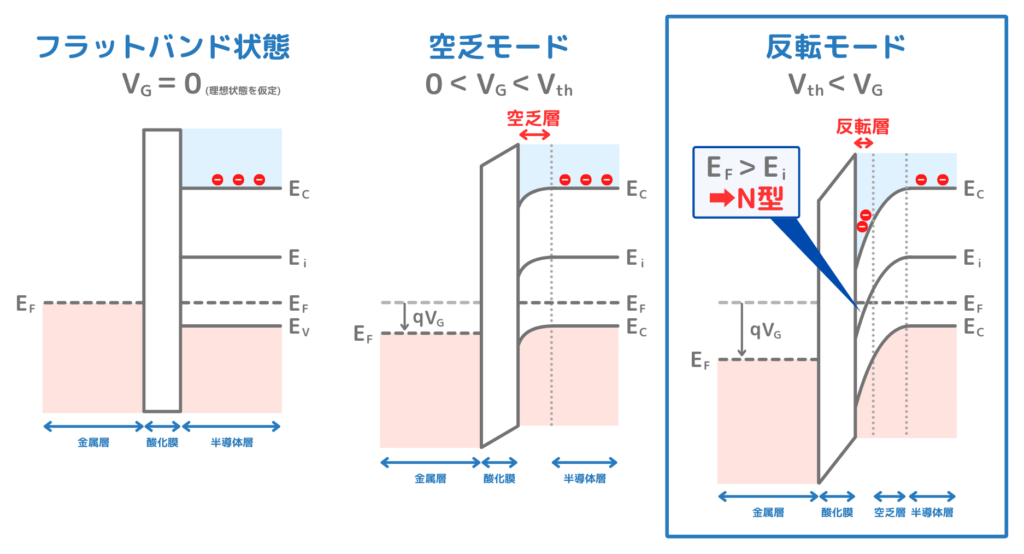

1.フラットバンド状態(VG = 0)

ゲート電圧が0Vのとき、金属・酸化膜・半導体に電界は発生せず、半導体表面のエネルギーバンドはほぼ平坦な状態になります。この状態をフラットバンド状態と呼びます。

フェルミ準位 EFはバルクと表面で一致しており、p型基板ではホールが多数キャリアです。表面にキャリアの偏りはなく、チャネルは形成されていません。

酸化膜(SiO2)は半導体に比べて非常に大きなバンドギャップを持つため、電子やホールは容易に通過できません。そのため、ゲートと半導体は電気的に絶縁されており、ゲート電圧は電界としてのみ半導体に作用します。

2.空乏モード(0 < VG < Vth)

ゲートに正の電圧を印加すると、金属ゲートが正に帯電し、その電界が酸化膜を介して半導体表面に作用します。

バンド図では電圧を電子のエネルギー(−qV)として表すため、金属ゲートに正の電圧を印加すると、金属側のフェルミ準位EFは下向きにシフトして描かれます。

p型基板の多数キャリアであるホールは表面から押し出され、イオン化したアクセプターのみが残った空乏層が形成されます。

空乏層では固定された電荷が分布するため、半導体内部の電位は位置によって変化します。この空間的な電位変化は、電子のポテンシャルエネルギーの変化としてバンド図に反映され、EC・EV・Eiが表面に向かって曲がって描かれます。

ただし、この段階ではまだ電子は多数キャリアにならず、表面に連続した電子の通り道(チャネル)は形成されていません。

3.反転モード(Vth < VG)

ゲート電圧をさらに大きくすると、空乏層の電位変化が増大し、半導体表面のバンドはさらに大きく曲がります。その結果、表面の真性準位Eiに対してフェルミ準位 EF が上に位置するようになります。

真性準位Eiは電子とホールの数が等しくなる基準であり、EFがEiより上に位置する場合、電子の占有確率が高くなるため、その領域はn型的であると判断できます。

この状態では、p型基板でありながら表面は n型に反転し、電子が多数キャリアとして半導体表面に蓄積されます。この電子が集まった層を反転層と呼びます。

反転層が形成されることで、ソース・ドレイン間をつなぐ電子の通り道(チャネル)ができ、MOSFETはON状態となります。