【半導体】成膜工程とは?手法と原理

成膜工程とは?

半導体の成膜工程は「ウェーハ上に半導体膜や配線膜、絶縁膜を形成する工程」です。

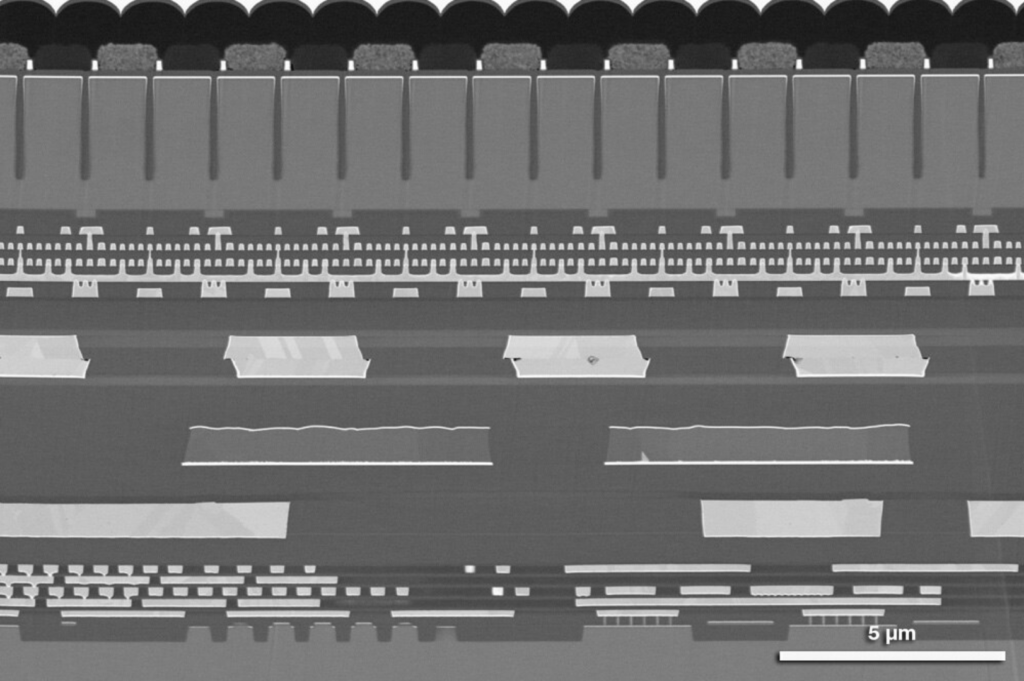

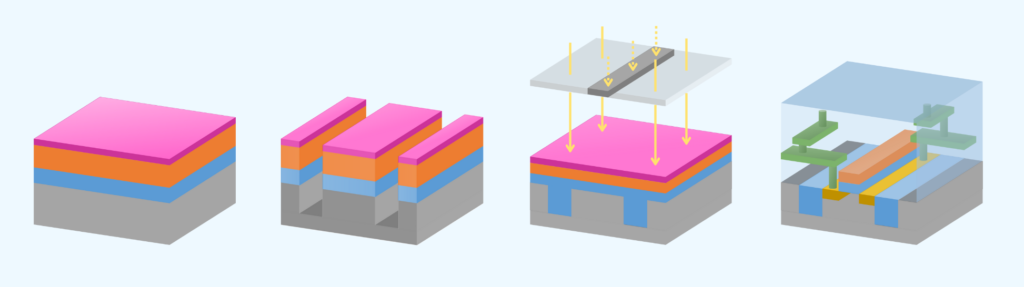

上は半導体素子の断面写真です。半導体素子は非常に多くの層から構成されていることが分かります。このような構造は「ウェーハ上に薄膜を形成した後、不要部を除去」を繰り返すことで形成されています。

微細な半導体素子の形成には「均一で薄い薄膜を形成可能な成膜工程」が非常に重要です。

成膜の材料

半導体の成膜工程では、以下の様な材料が成膜されます。

- 絶縁膜(酸化膜)

- 金属膜

- ポリシリコン膜

- 保護膜

SiO2など、素子間の絶縁分離やゲート絶縁に必要な膜。

AlやCuなど、配線を形成するための膜。

低抵抗率のであり、MOSFETの金属電極として使用される。

SiO2やSi3N4など、半導体素子を物理的・化学的に保護する膜。

成膜方法

成膜は大きく以下の4つの方法があります。

- 熱酸化

- CVD(化学気相成長)

- PVD(物理気相成長)

- メッキ法

1つずつ成膜の原理を解説します。

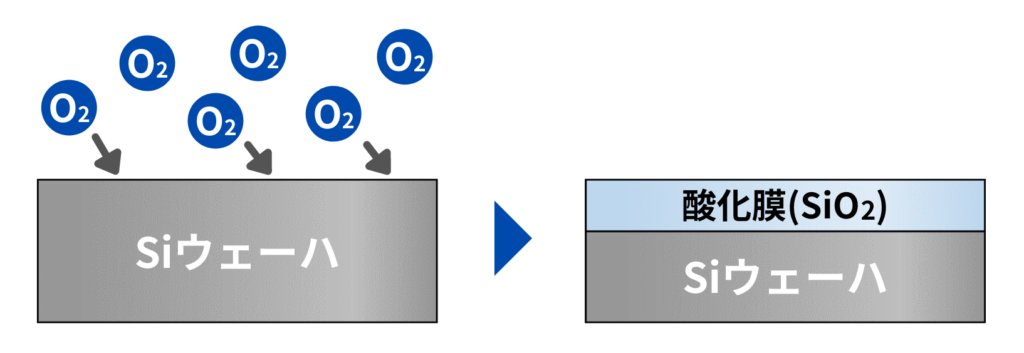

熱酸化法

熱酸化法は「ウェーハを酸素雰囲気や水蒸気中で加熱することで表面を酸化し、酸化膜(SiO2)を形成する方法」です。

熱酸化では酸化炉を用いて、ガスを流しながらウェーハを加熱します。

熱酸化には、使用するガスの種類・形態によってドライ酸化・ウェット酸化などが存在します。

CVD(化学気相成長)

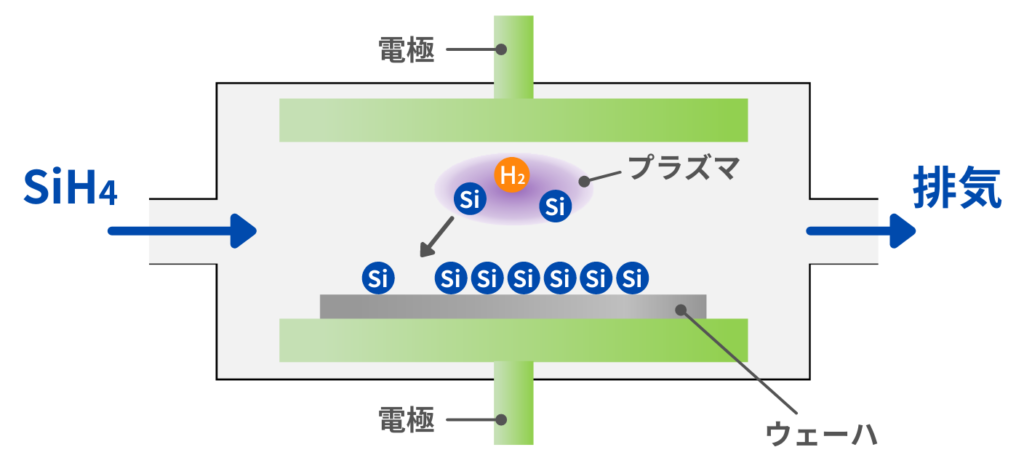

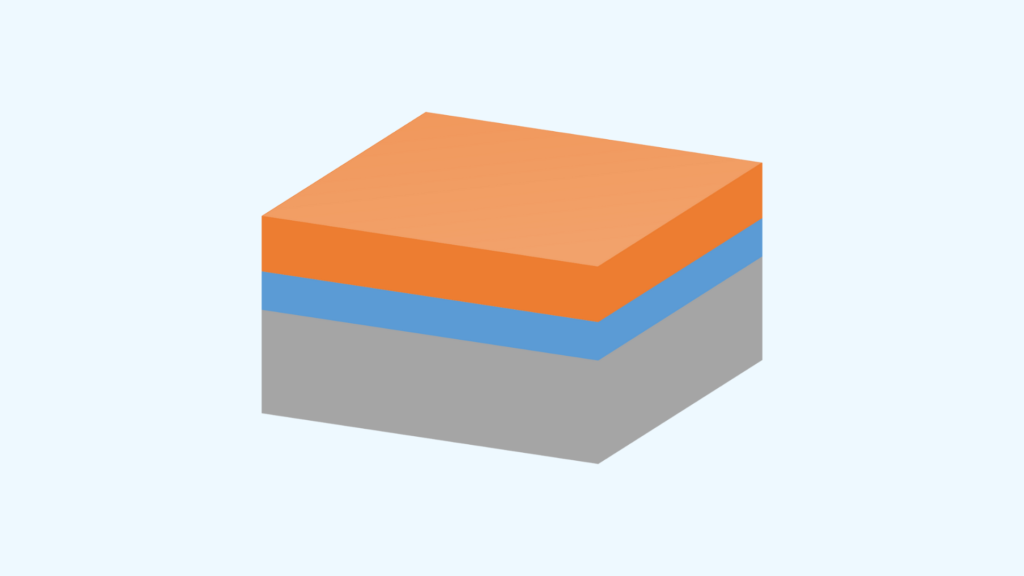

CVD(化学気相成長)は「気体原料とウェーハ間の化学反応によって、ウェーハ表面に材料薄膜を形成する、または、気相中の化学反応で生成した材料をウェーハ上に堆積する方法」です。

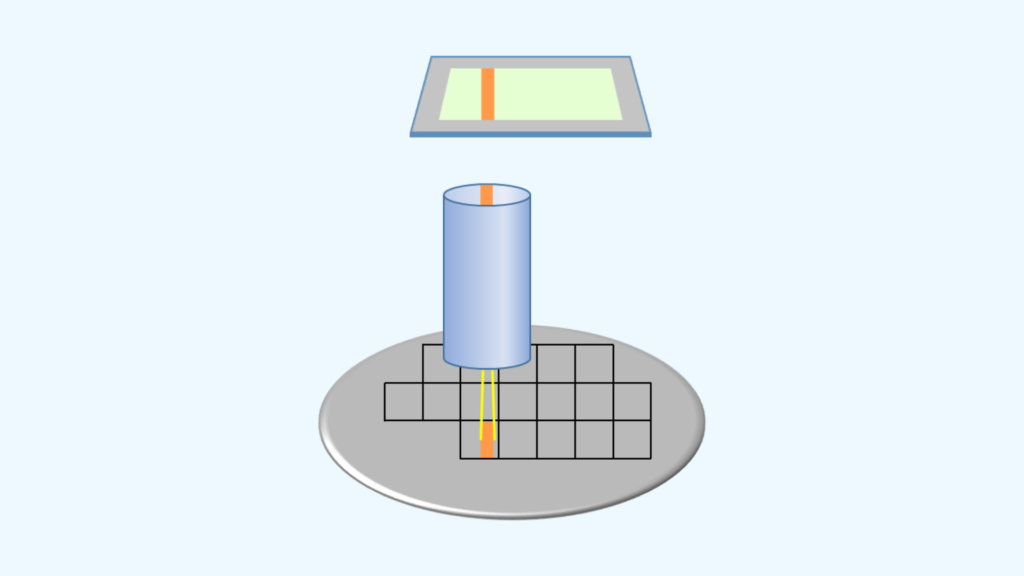

CVDでは、原料ガスにエネルギーを与えて分子を解離させ、解離生成物を基板に付着させることで成膜が進行します。

例えば上図では、シランガスSiH4を原料に、プラズマにより生成したSi粒子がウェーハ表面に付着することが薄膜が形成されています。

CVDは原料ガスへのエネルギー供給方法によって、「熱CVD」と「プラズマCVD」に分類されます。

PVD(物理気相成長長)

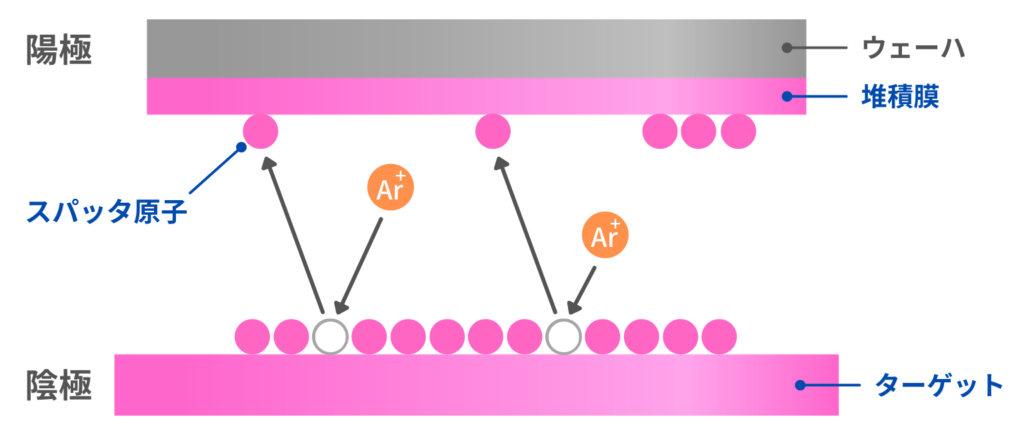

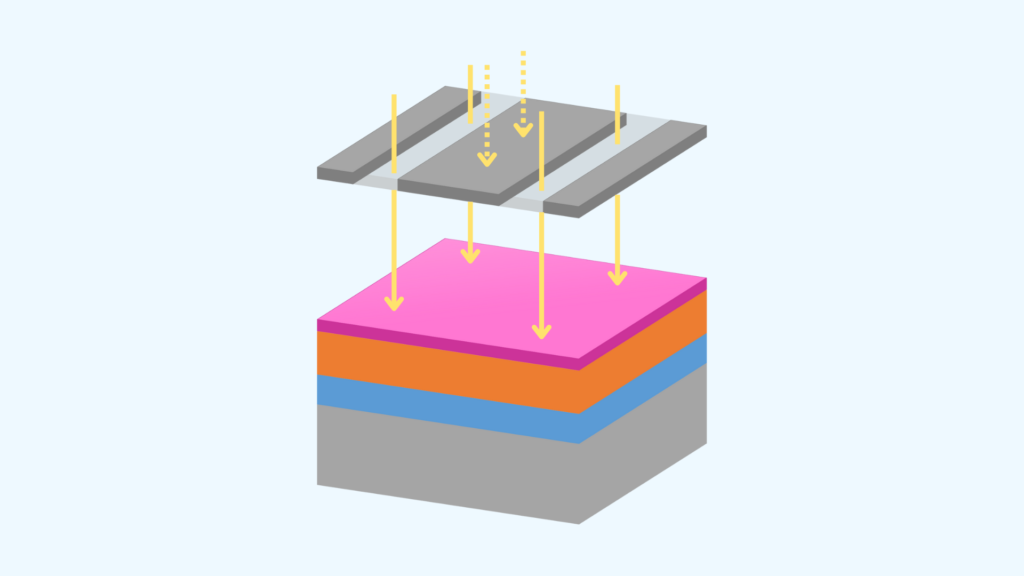

PVD(物理気相成長)は「原料を加熱・スパッタ・イオンビーム照射などにより蒸発・飛散させ、ウェーハ表面に物理的に堆積させる成膜方法」です。

薄膜としたい材料を物理的に蒸発させるため、物理気相成長と呼ばれています。

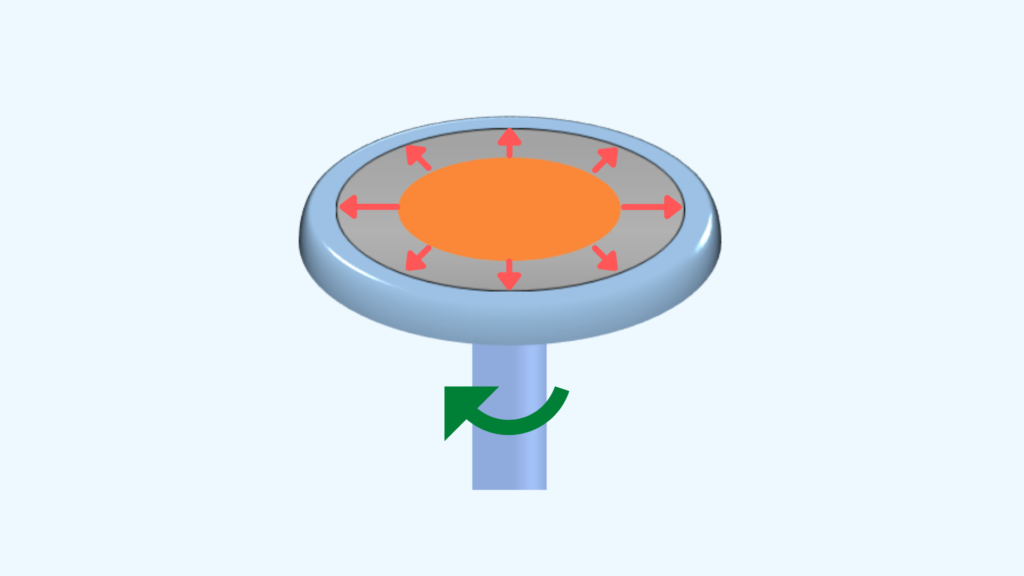

上図は半導体製造で最も一般的なPVDであるスパッタリングの模式図です。真空中で成膜したい材料(ターゲット)にAr粒子を高速で衝突させ、叩き出されたターゲット粒子をウェーハに付着・堆積させることで成膜されます。

他にも、PVDは材料の飛散方法により「スパッタリング」「蒸着」「イオン化蒸着」「イオンビーム」などに分類されます。

メッキ法

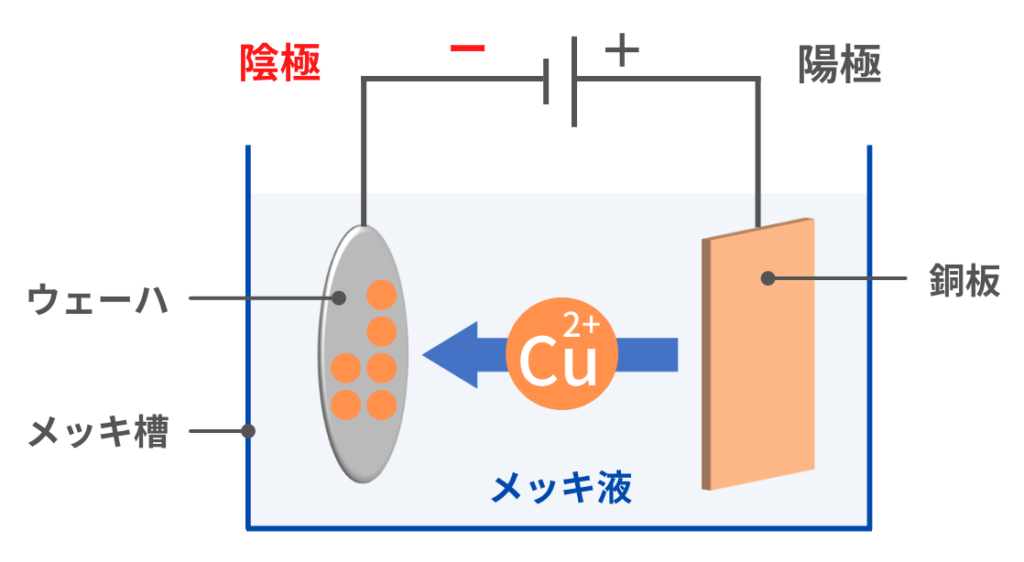

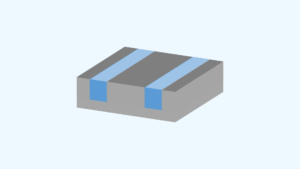

メッキ法は「ウェーハを陰極、銅板を陽極にして電流を流すことで、ウェーハ表面に銅薄膜を析出させる方法」です。

硫酸銅(H2SO4)などのメッキ液に、ウェーハを陰極、銅板を陽極とし電流を流すことで、酸化還元反応によりウェーハ表面にCu薄膜が成長します。

アノード(陰極)反応:Cu→Cu2++2e-

カソード(陽極)反応:Cu2++2e-→Cu

Cu成膜はスパッタ法などでも得られますが、材料コストが安く生産性も高いことから、半導体の配線工程では主にメッキ法が用いられています。