【図解】半導体製造工程の流れ

半導体素子はいくつもの工程を経て製造されています。ここでは、半導体素子の基本構造であるMOSFETの製造を例に、工程フローの一例を順番に解説します。

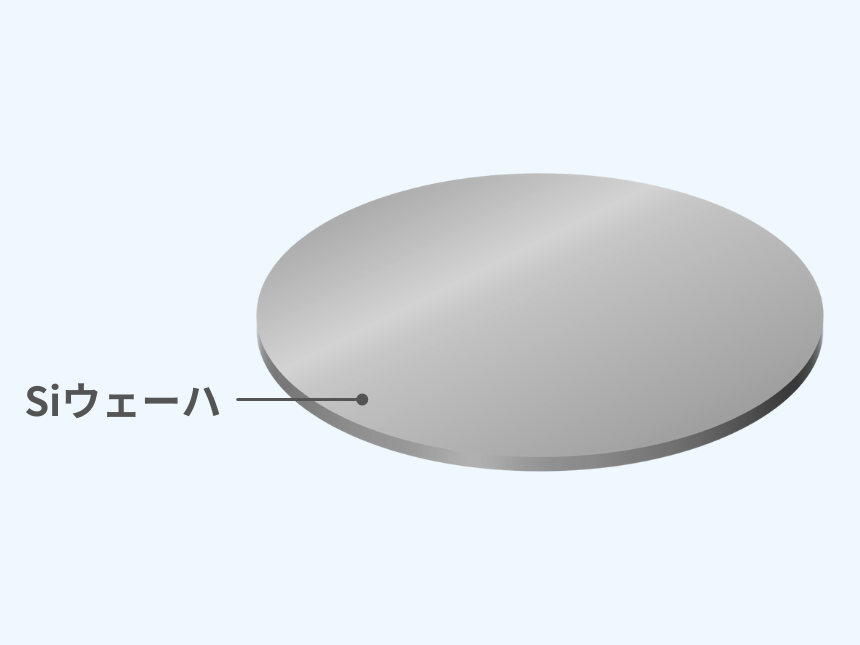

シリコンウェーハ製造

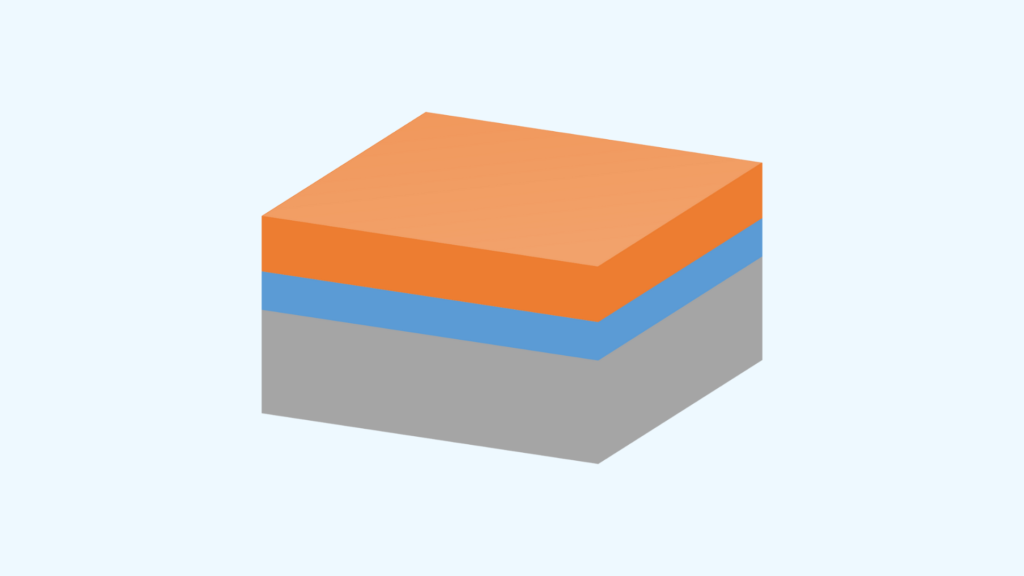

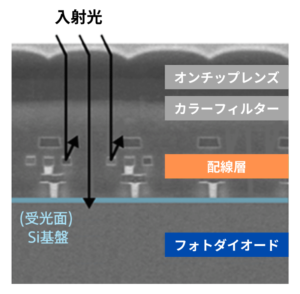

単結晶シリコンインゴットをスライスし、研磨することで超平坦・鏡面のシリコンウェーハを製造します。半導体製造ではウェーハに回路を刻んでいきます。

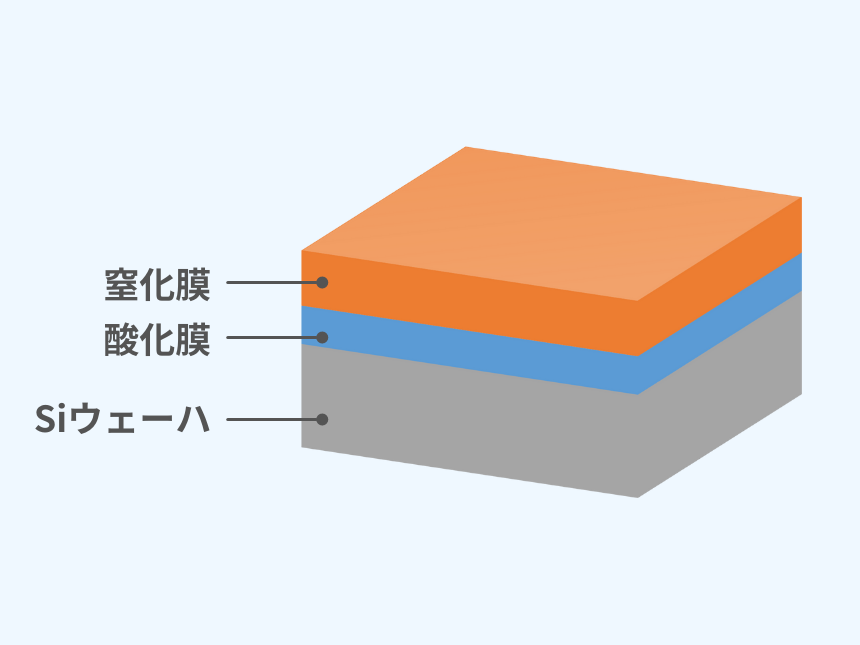

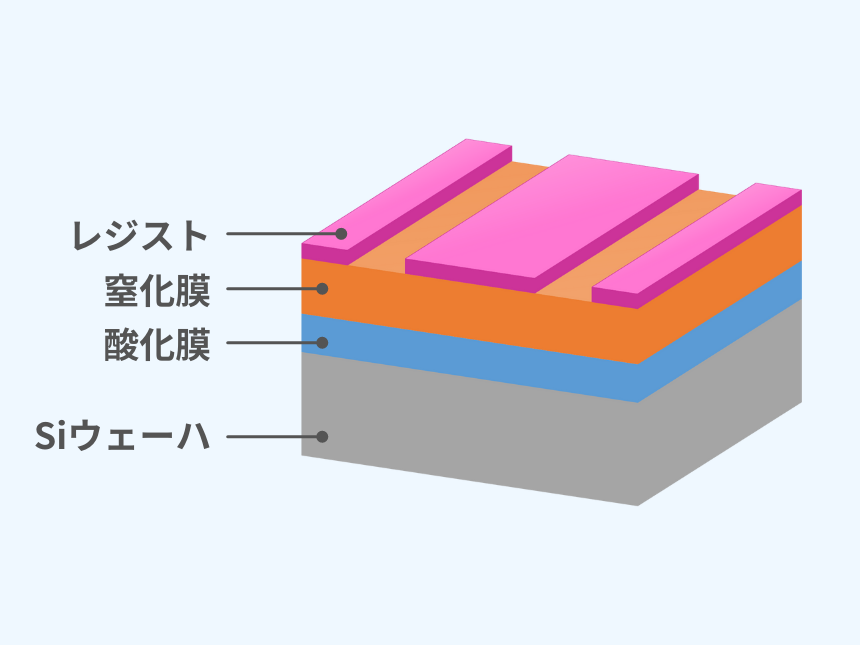

酸化膜/窒化膜成膜

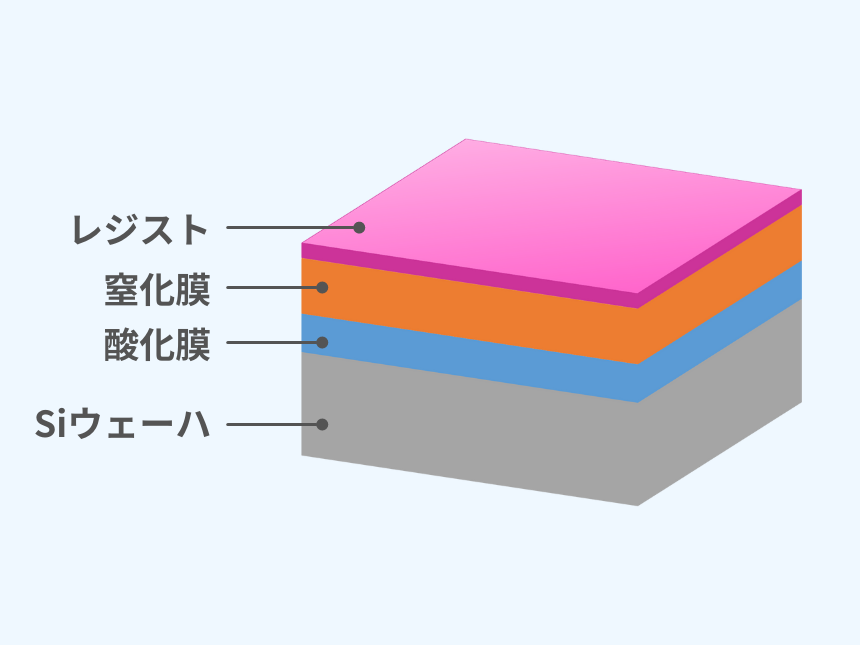

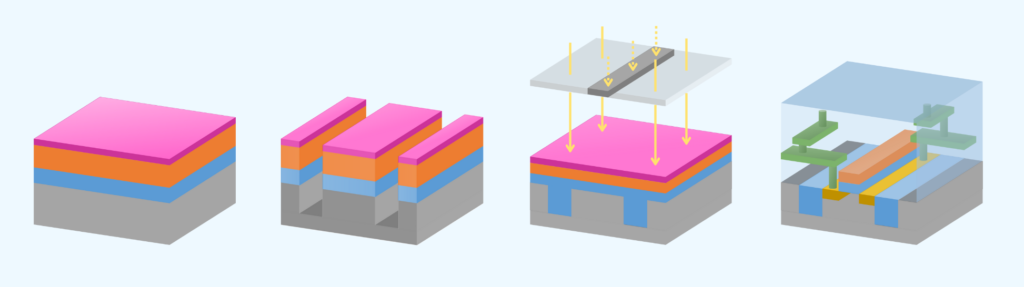

フォトレジスト塗布

スピンコート法によりフォトレジスト(PR)を塗布します。レジストはフォトリソグラフィー工程でのエッチングマスクになります。

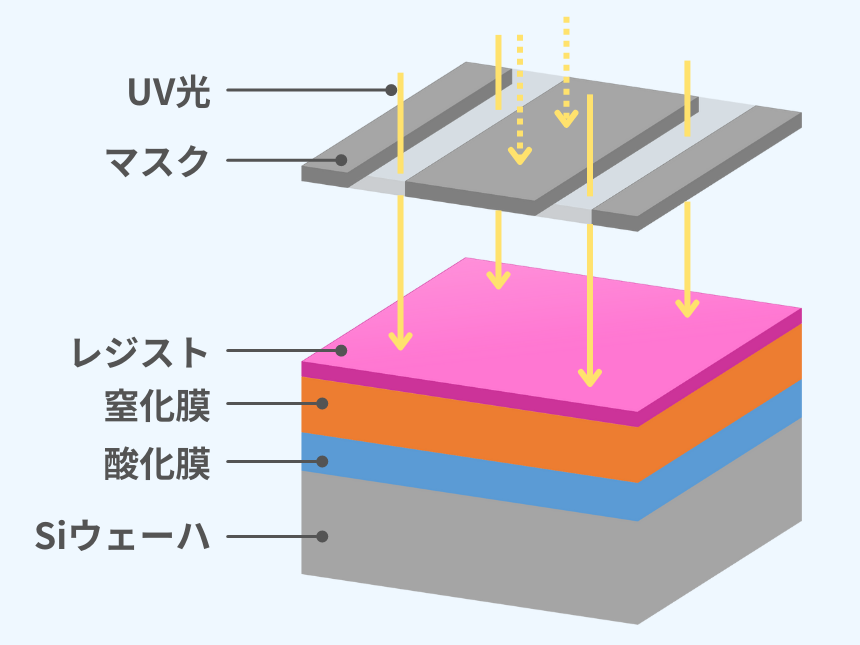

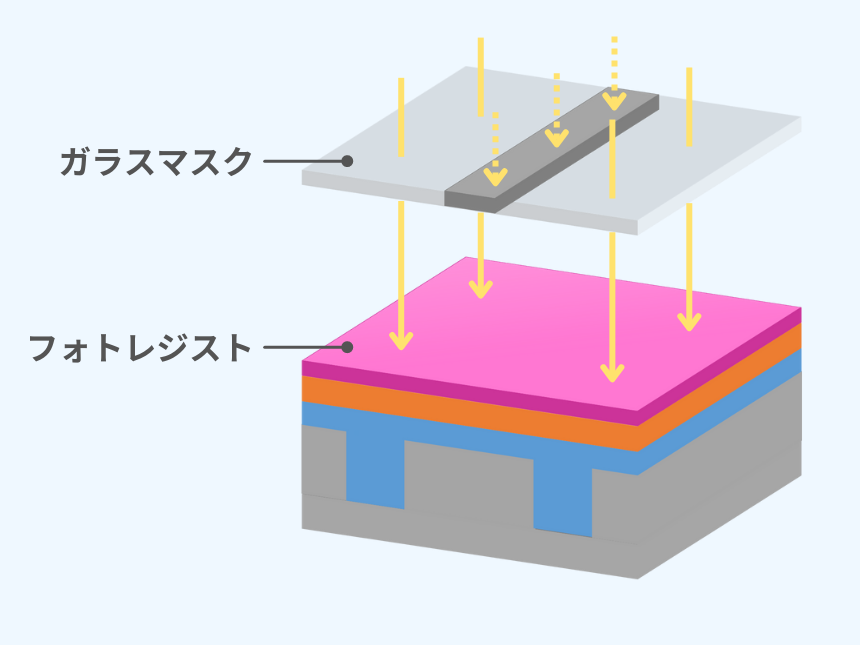

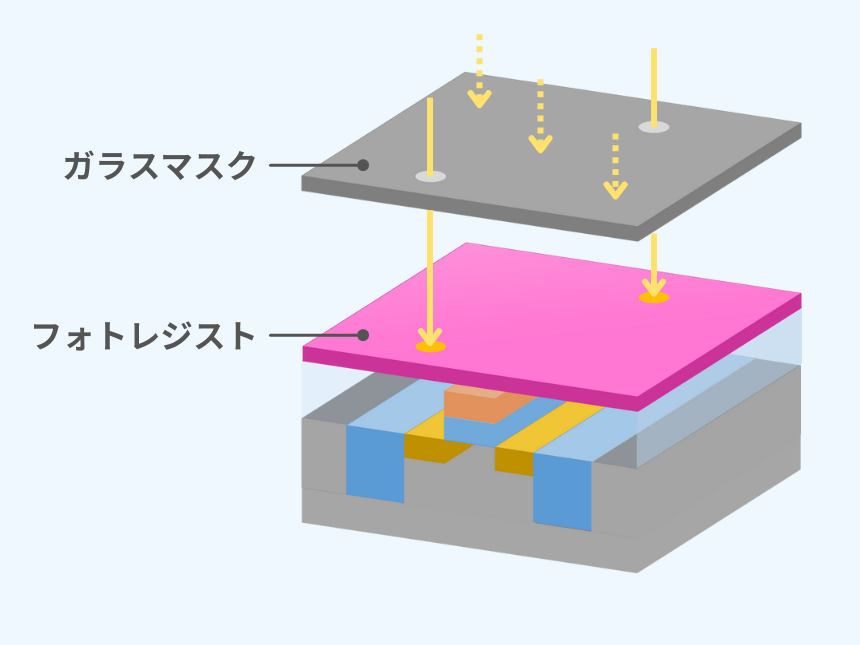

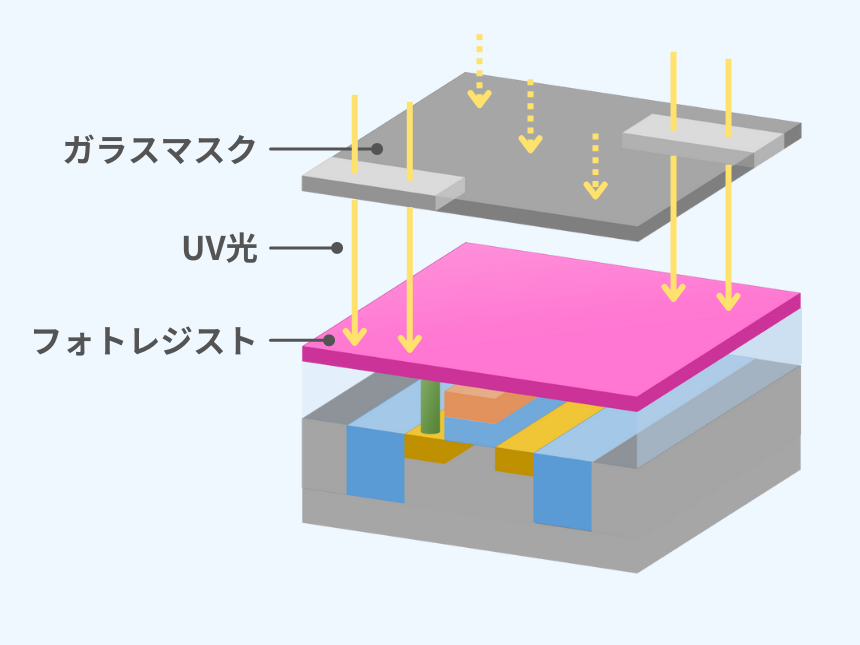

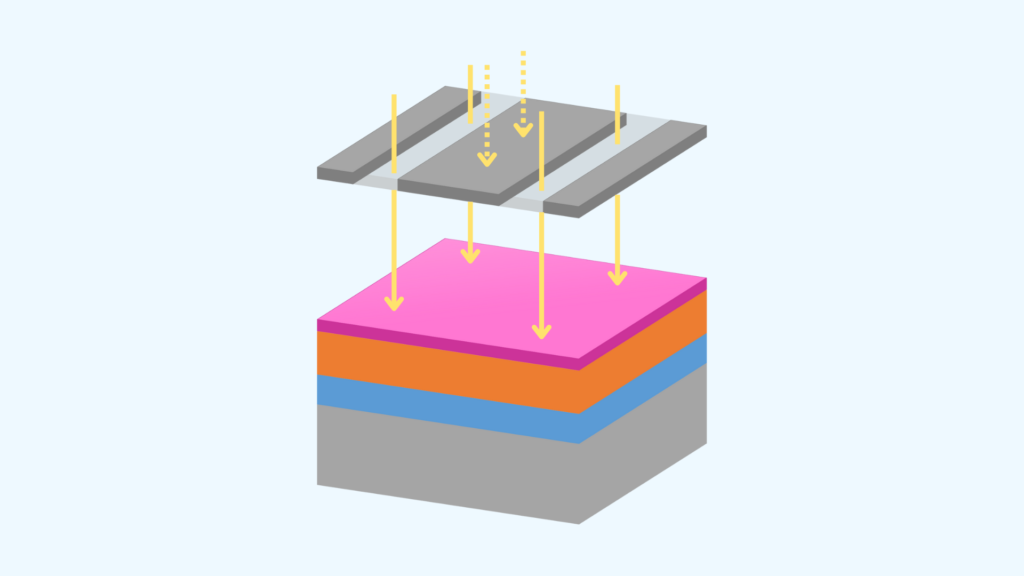

露光

回路が描かれたマスクを通し、ウェーハにUV光を照射します。光照射部はレジストの溶解性が変化し、続く現像工程で不要なレジストが除去されます。

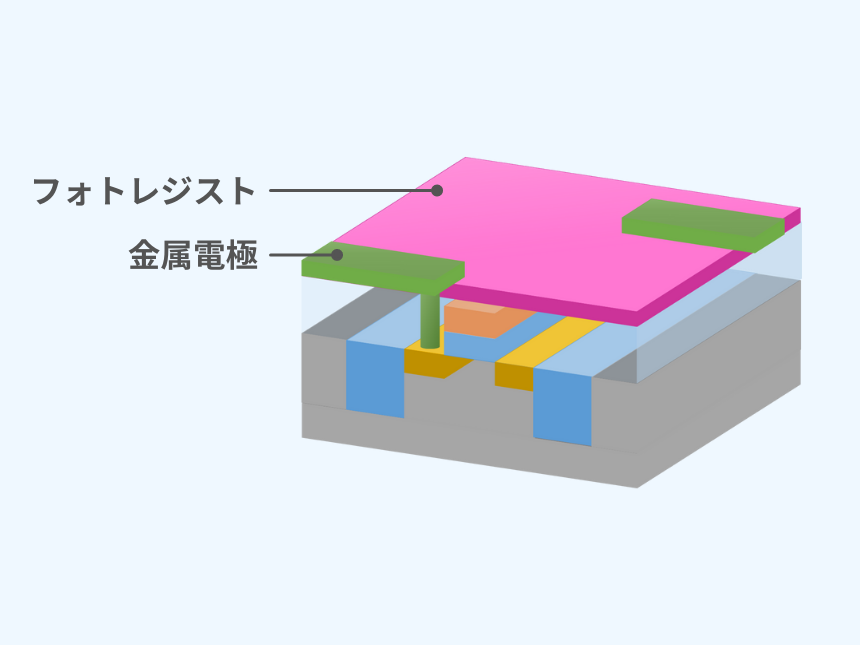

現像

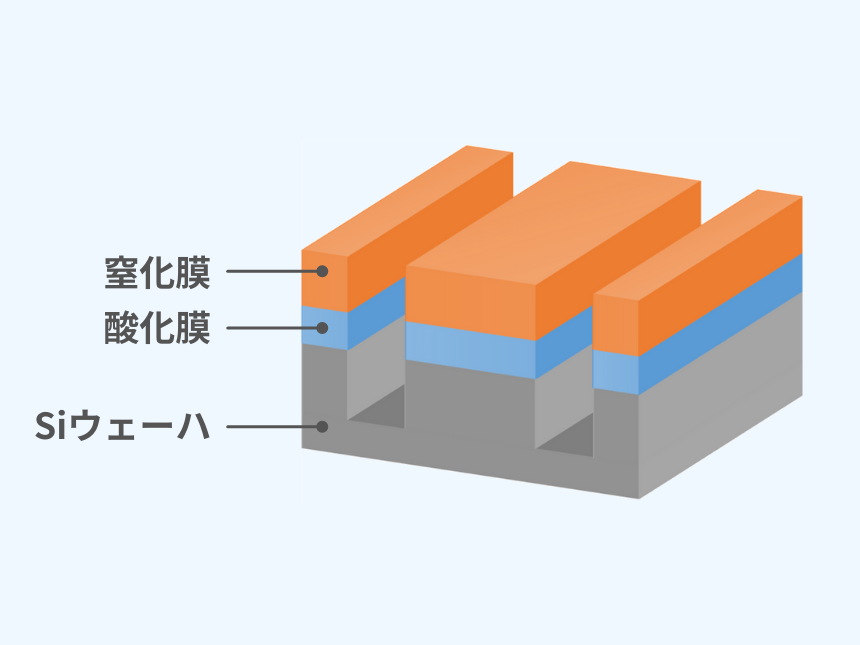

エッチング

レジストをマスクとして、エッチングにより不要部を除去し回路を形成します。

エッチングには様々な種類がありますが、デバイス工程では選択性が高い「反応性イオンエッチング(RIE)」が多用されます。

レジスト剥離・洗浄

不要なレジストを剥離し除去します。

レジスト除去には「薬液を使用するウェット方式」と「気体として除去するアッシング(灰化)」があります。デバイス工程では選択性の高いアッシングが多用されます。

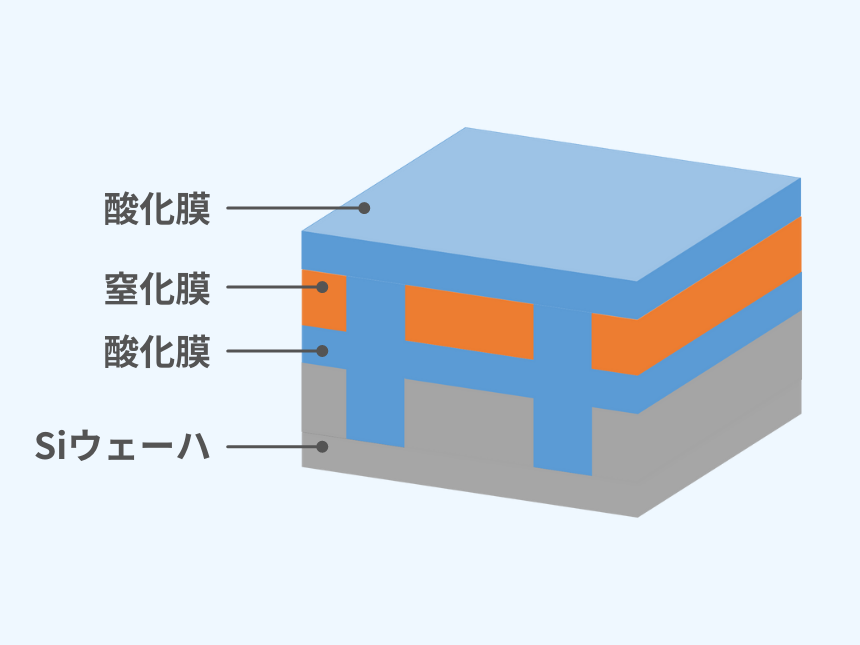

絶縁膜埋め込み

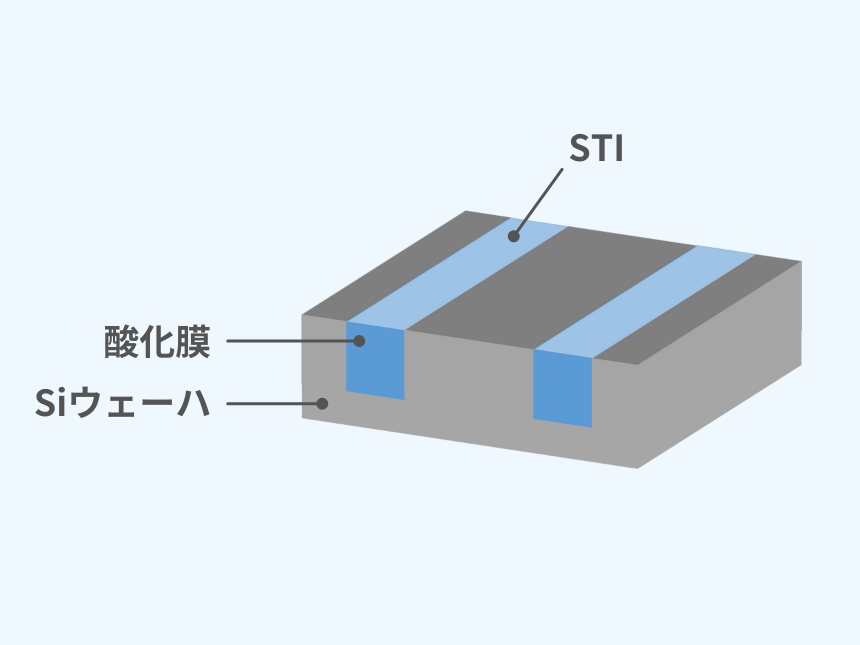

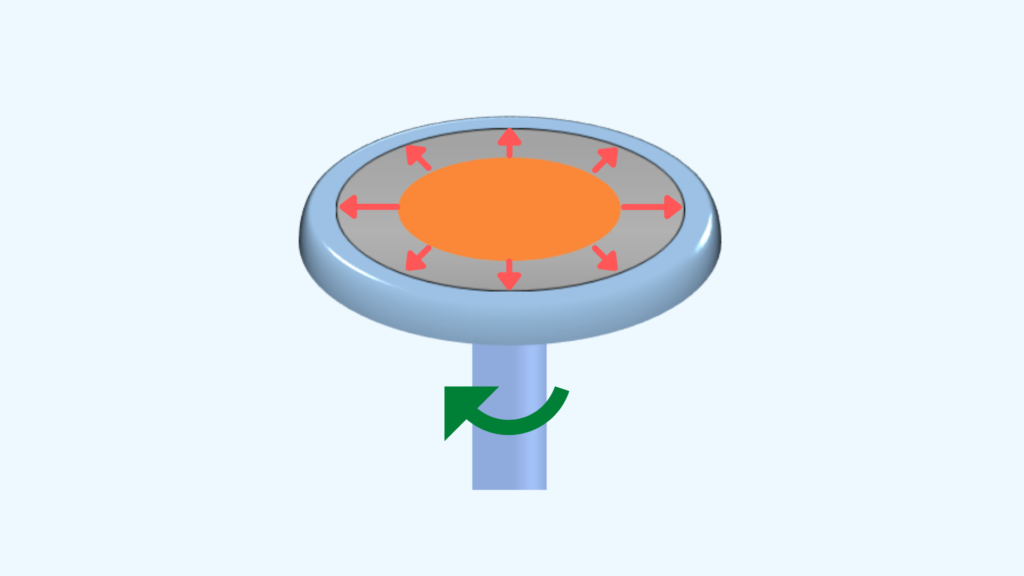

平坦化

機械化学研磨(CMP)により不要部を研磨し平坦化します。

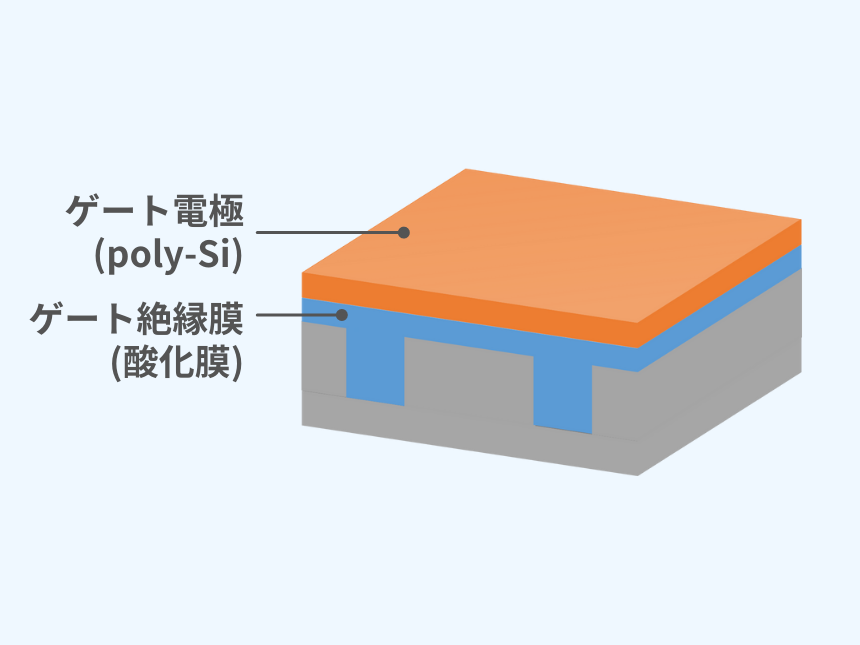

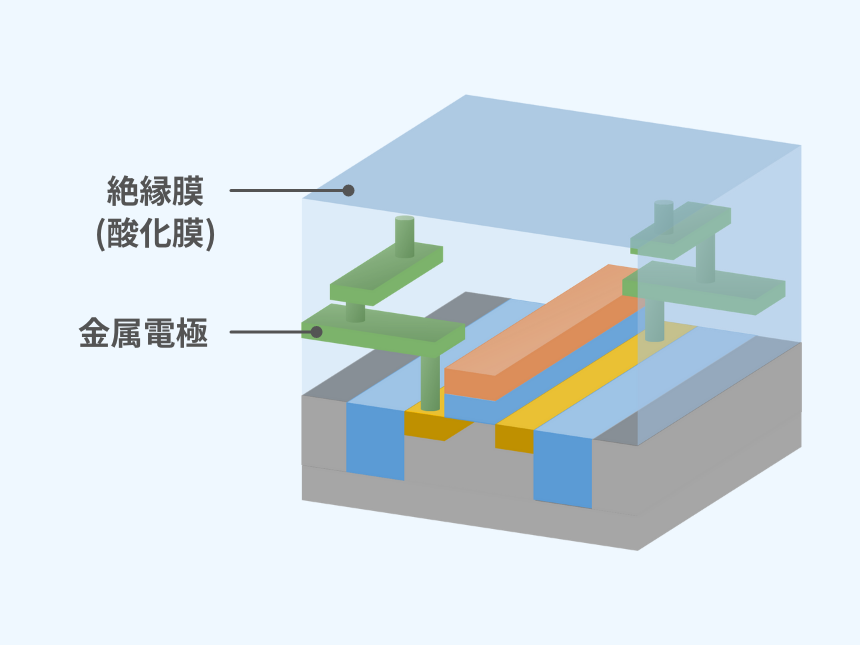

ゲート酸化膜/ゲート電極形成

熱酸化でSiを酸化し、ゲート酸化膜を形成します。ゲート酸化膜表面に窒化処理を施した後、CVDでゲート電極層(多結晶シリコン(poly-Si))を形成します。

パターン形成

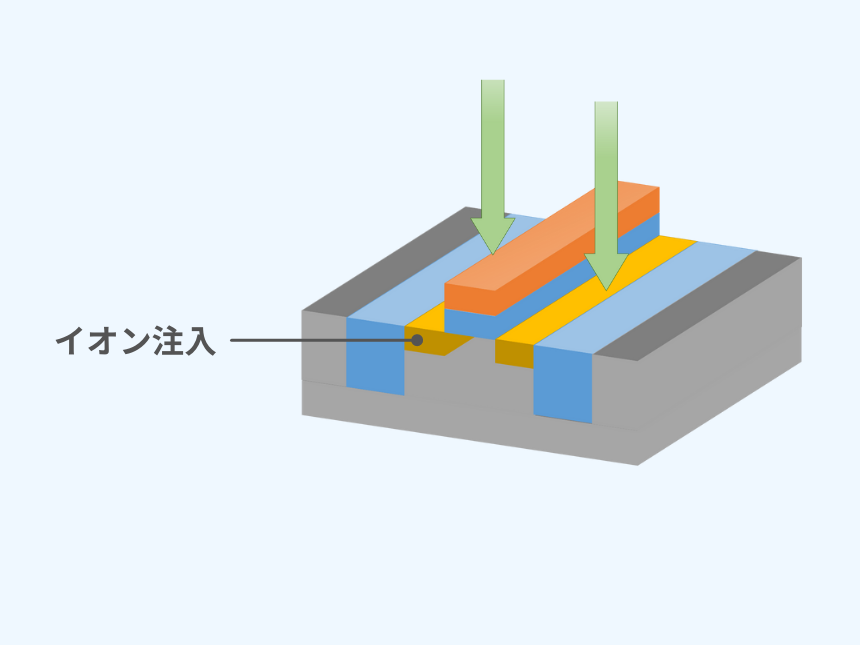

イオン注入

ソース・ドレイン領域にイオン注入によりドーパントを打ち込みます。酸化膜(STI)部にはイオンが打ち込まれません(犠牲酸化膜)。

その後、回復熱処理によりドーパントを活性化します。

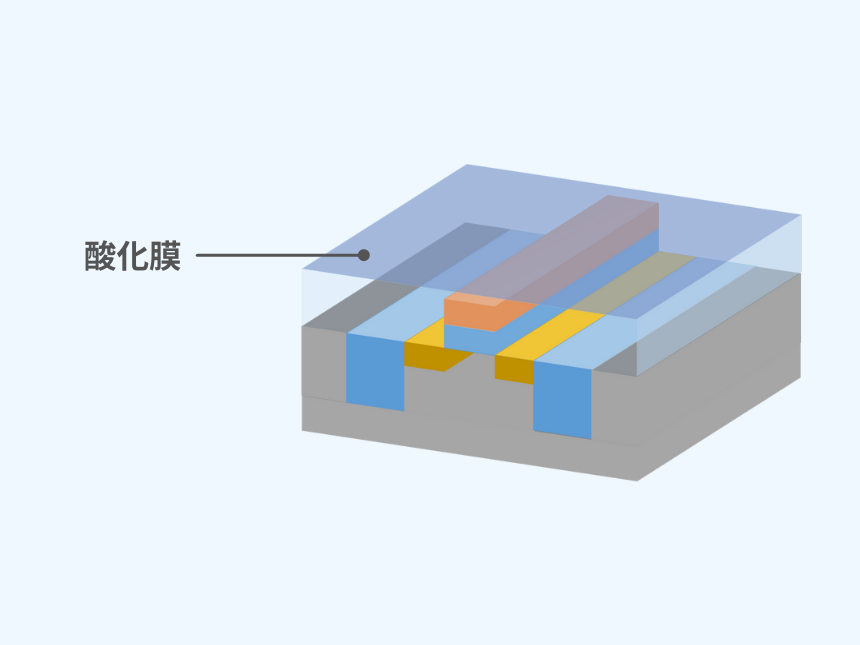

層間絶縁膜形成/平坦化

CVDにより酸化膜を堆積します。この酸化膜は絶縁層として機能します。

コンタクトホール形成

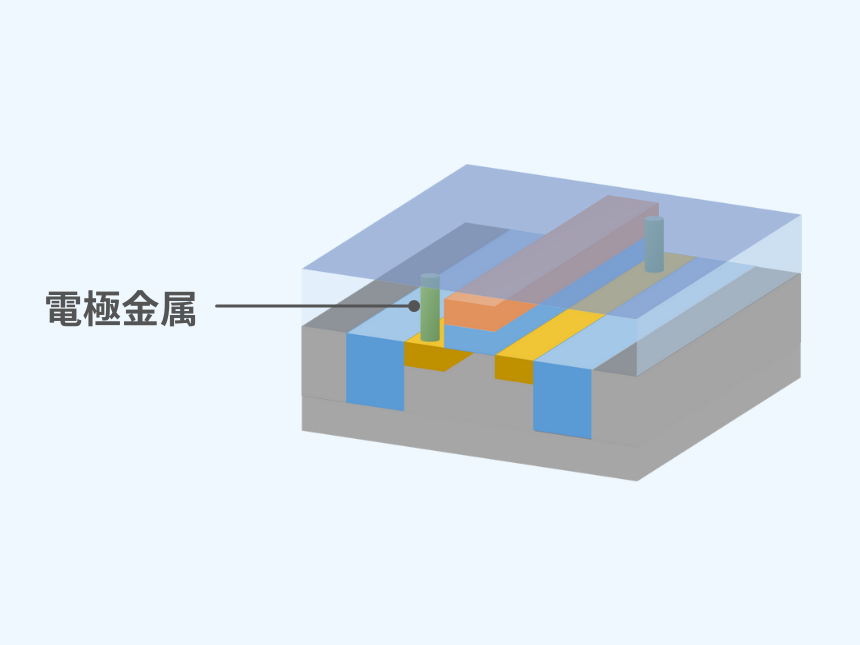

コンタクト形成

トレンチ形成

金属膜堆積

配線形成

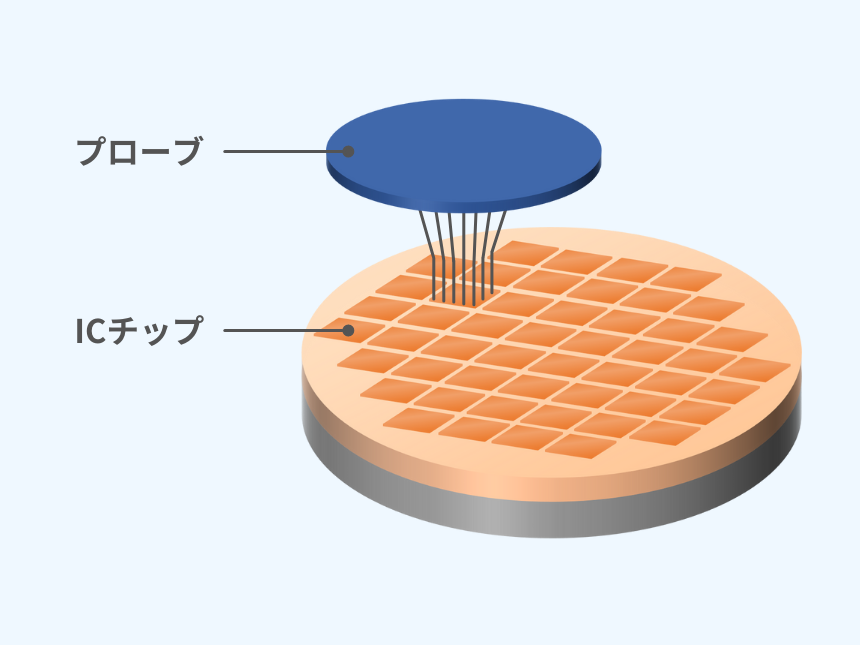

プローブ検査

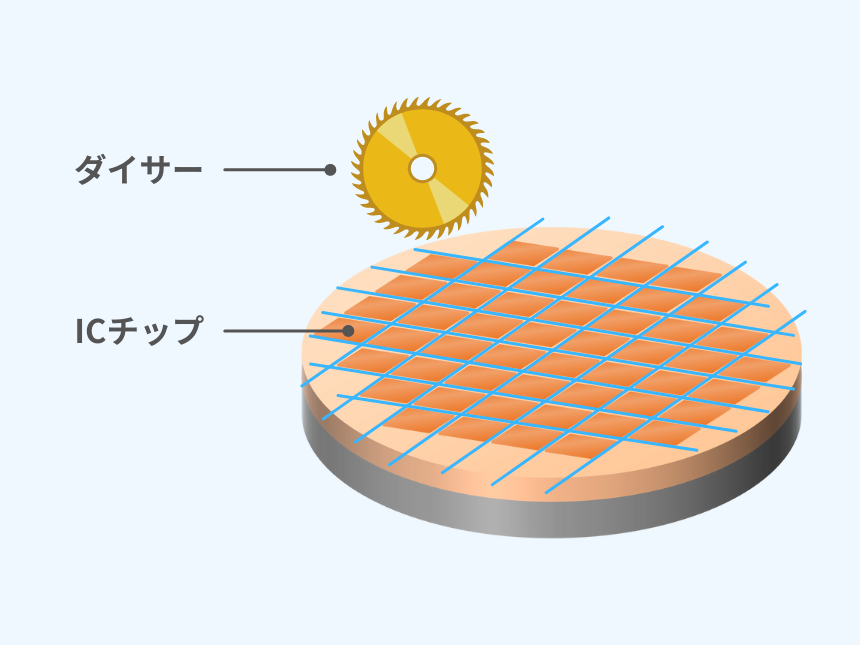

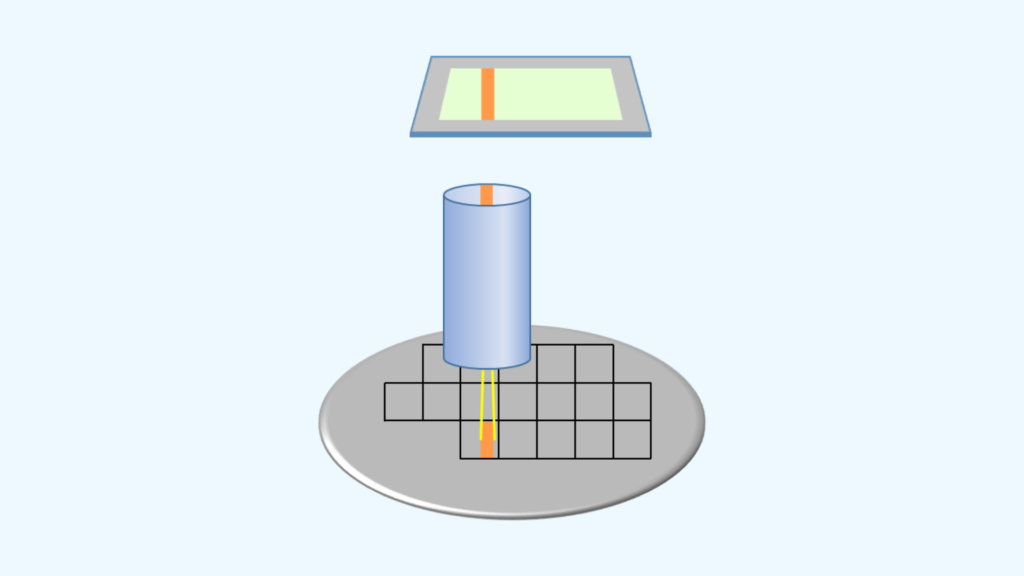

ダイシング

回転するダイヤモンドブレードでチップ(ダイ)を切断します。

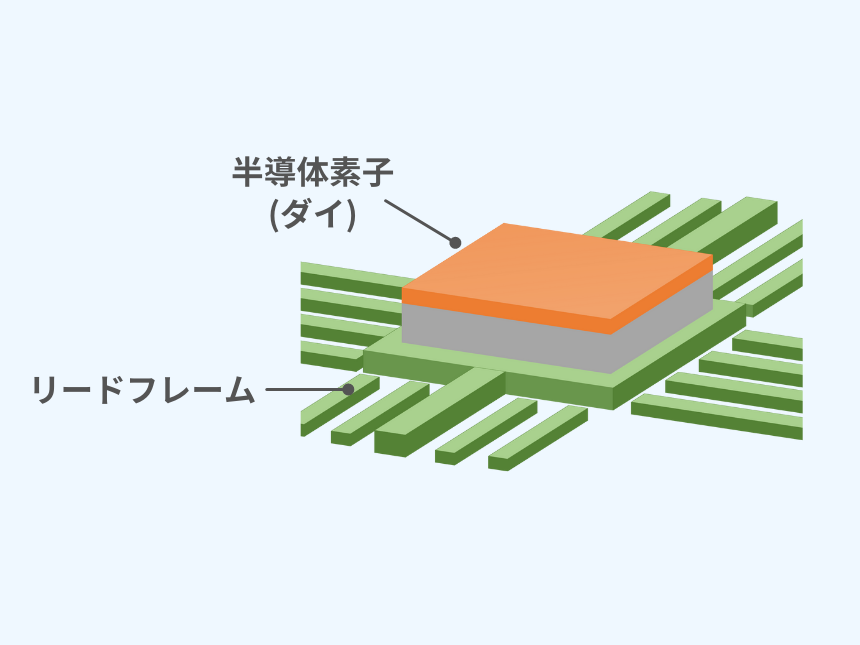

ダイボンディング

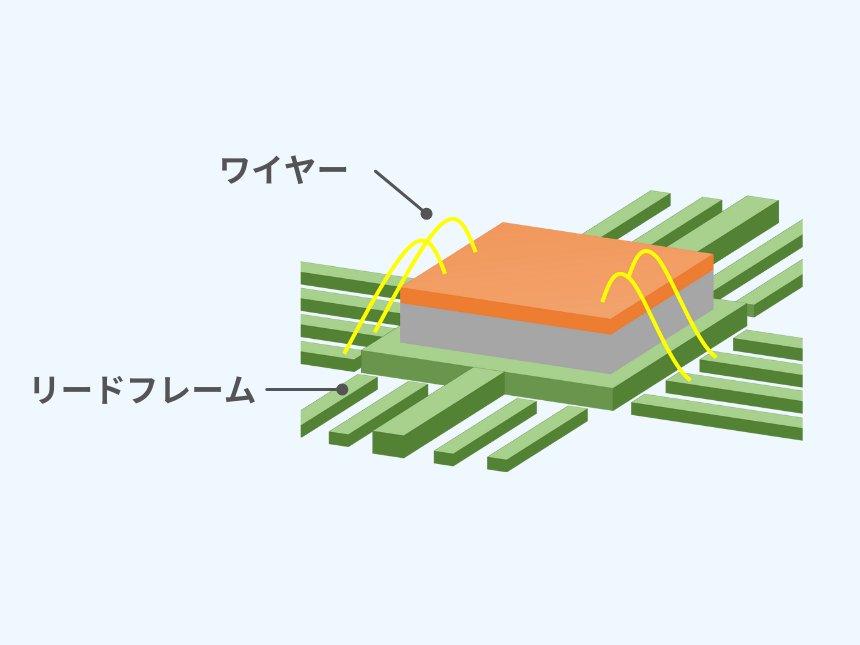

ワイヤーボンディング

半導体素子と基板のインナーリードを金線で接続します。

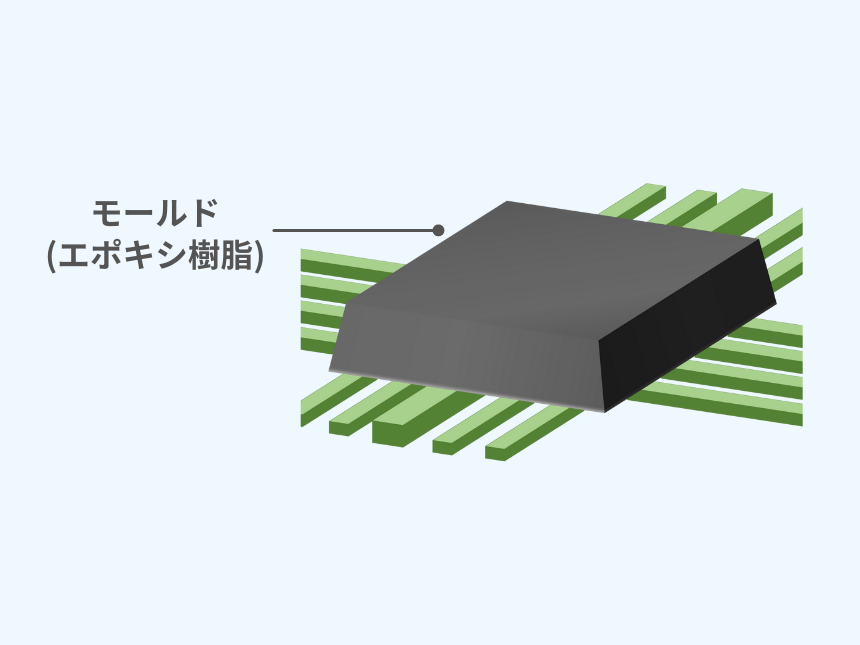

モールディング

半導体素子をエポキシ樹脂で封止します。素子を衝撃や水分から守る役割があります。

ウエーハが丸いのは品質の均一化のためですか?半導体は角型なので最初から角型にしてはいけないのですか?今回の記事をみて半導体が少し理解出来ました 80歳女性です!

コメントありがとうございます。

シンプルな回答としては半導体の材料であるシリコンインゴットが円柱状だからです。

単結晶の育成には熱環境の制御が非常に重要です。熱環境が不安定(まばら)な場合、冷えた箇所が次々と結晶化してしまい、単結晶ではなく多結晶となってしまいます。

シリコンインゴットを作製するCZ法では、るつぼ内に溶解したSiメルトに種結晶と呼ばれる単結晶を沈め、回転させながらゆっくりと引き上げることで単結晶を得るため、円形となります。

均一な熱分布を形成するためには円形のヒーターが適していますし、結果として結晶も円形になるものだと思います。

結晶周方向の品質を均一化するために結晶を回転させていることも、ウェーハが円形である理由の1つだと思います。

また、シリコンウェーハ製造やデバイス工程で使用されるCMPはウェーハを回転させながら研磨するため、円形の方が全面を均一に研磨できると思います。

長くなりましたが、単結晶作成と、デバイスを作製する際の面内品質の均一性から、ウェーハは円形となっているのでしょう。

半導体の理解のために当サイトを見ていただき、本当にうれしく思います。80歳でも豊富な知的好奇心に、感銘を受けました、今後も当サイトを見ていただけると嬉しいです!

この工程ごとに別々の装置があるのでしょうか?

まとめて一つの装置でできたりしないのでしょうか?

コメントありがとうございます。

以下の理由から、装置を1つにまとめることは難しいと思います。

➀まとめるメリットがない

半導体製造工程は極めて工数が多く複雑です。その中で、最終的なデバイスの歩留まりを高めるように管理しています。

そのため、半導体デバイス企業では、各装置の管理・メンテナンスを日常的に行っています。装置が1つにまとまっていると、歩留まり悪化の要因解析が難しく、また、メンテナンスも困難になります(メンテナンスの度に全工程が止まることになります)。

また、一部装置の入れ替えも不可能となり、不便です。

➁技術力

半導体製造装置製造には極めて高い技術力が必要です。工程ごとに強い企業/弱い企業があります。

すべての工程を網羅する技術力を持つ企業は存在せず、1つの企業で、全ての工程をまとめた装置を製造することはできません。

➂装置が超巨大になる

半導体プロセスは数百を超える工程からなります。半導体製造装置を全てまとめたとしても、装置が超巨大となってしまいます。

装置の搬入・設置や、日常のメンテナンスが極めて大変であり、まとめるメリットはないでしょう。

なお、工程の一部をまとめた装置もあり、フォトレジスト工程におけるレジスト塗布と現像装置をまとめたコーダデベロッパが代表例です。

半導体のフォトリソグラフィとは?工程フローと原理

解説いただきありがとうございます。

素人質問で大変恐縮なのですが、図示いただいている工程だけを見ると、直接シリコンウエハを回路の形にエッチングすればいいように見えてしまうのですが、技術的に難しいということなのでしょうか?

また、質問に回答しているところで、コータデベロッパが一体化しているとのことですが、間に挟まれている露光工程と一体化するという流れはないのでしょうか?露光はASMLさんが専業でやられているからということでしょうか、それとも性質上難しいのでしょうか。

お手数をおかけしますが、ご回答いただけますと幸いです。

コメントありがとうございます。以下、回答いたします。

Q1.図示いただいている工程だけを見ると、直接シリコンウエハを回路の形にエッチングすればいいように見えてしまうのですが、技術的に難しいということなのでしょうか?

A1.原理的には可能ですが、コスト・スループットの観点から採用が難しいでしょう。電子線リソグラフィー(電子ビーム直接描画)の開発も行われており、フォトマスクが不要という長所がある一方、スループットが低いという欠点があります。結果として、現在のフォトリソグラフィーが量産されています。他方、リソグラフィー用マスク、先端原理試作品、ナノスケール科学研究開発用といった1点物の製作には利用されているようです。

Q2.コータデベロッパが一体化しているとのことですが、間に挟まれている露光工程と一体化するという流れはないのでしょうか?

A1.推測ですが、スピンコートや洗浄等の溶液系が必要なコータデベロッパと、光学系である露光装置を一体化することは難しく、メリットがないためでしょう。コータ・デベロッパはそれぞれ、レジストを塗布・除去する装置で、スピンコートや洗浄など装置の共通点が多く、一体化するメリットがあります。一方、露光装置は極めて精密な光学系・機構が求められます。そのため、溶液系の装置との一体化のメリットがありません。また、求められる技術も全く異なるため、一体化の動きはないでしょう。

分かりやすい解説ありがとうございます。

1点質問です。フォトリソでパターンニングした後、金属膜を成膜し、リフトオフする際、レジスト剥離液に浸漬するだけの方法が一般的でしょうか?もしくは、超音波にかけたりするのでしょうか?

コメントありがとうございます。以下、回答いたします。

レジスト剥離液に浸漬するだけか、超音波を印加するのか、どちらが一般的かは断言できません。ダイトロンの枚葉式リフトオフ装置では、レジストを剥離液に浸漬したのち、超音波(MS/US)とJET処理で物理的にレジストポリマーを除去すると記載があります。

枚葉式リフトオフ装置(ダイトロン株式会社)

また、ダルトンのリフトオフ装置では、剥離液への浸漬時に、超音波・揺動・液中JETを組み合わせて剥離させると説明されています。

リフトオフ HU型(量産向け)(ダイトロン株式会社)

リフトオフ装置のご紹介 HU型(ダイトロン株式会社)

非常にわかりやすい解説でありがとうございます。

それぞれの工程において、どんなメーカのどんな装置が使われているのか、ランキングなどのデータがもしあれば大変助かります。

Ceoi様

コメントありがとうございます。半導体・製造装置など業界ごとあればこちらのページにまとめています。

半導体業界研究

また、各製造装置ごとのシェアであれば、下記の記事が参考になります。

日本の前工程装置のシェアはなぜ低下?(EETimes)