なぜCMOSは低消費電力なのか:CMOS・PMOS・NMOSインバーターの比較

CMOSが低消費電力な理由は「入力電圧に応じてpMOS・nMOSのどちらかがOFF状態となるため、VDDからアースへの電流が流れないため」と説明されます。

この意味をCMOS・PMOS・NMOSインバーター回路を比較しながら考えてみましょう。

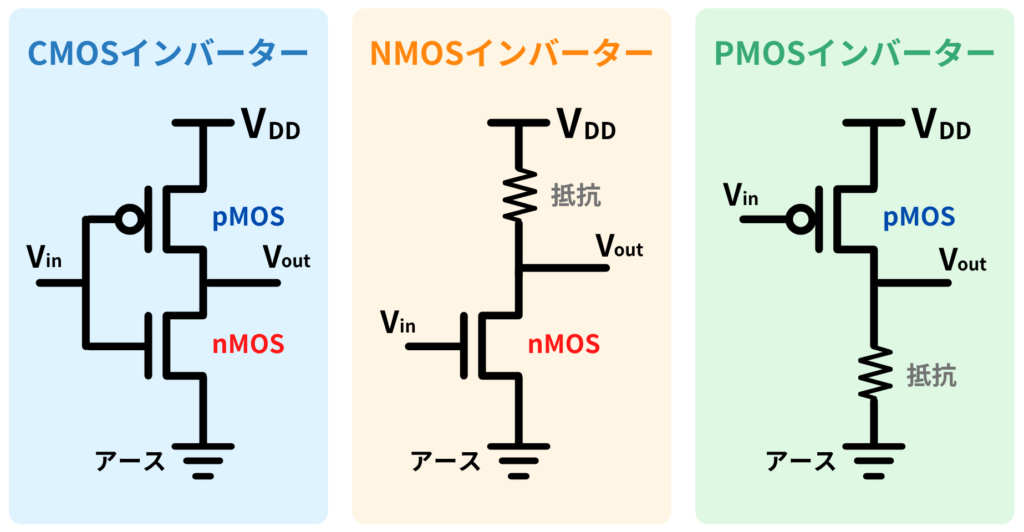

CMOS・PMOS・NMOSインバーターの構造

インバーター回路(NOT回路)は、構成方式により以下の3つに分類されます。

- CMOSインバーター(Complementary MOS)

- NMOSインバーター(単体NMOSロジック)

- PMOSインバーター(単体PMOSロジック)

nMOSFETとpMOSFETを組み合わせた回路

nMOSFETと抵抗を組み合わせた回路

pMOSFETと抵抗を組み合わせた回路

MOSFETをスイッチング可能な抵抗と考え、pMOSを通常の抵抗に置き換えたのがPMOSインバーターです(NMOSも同様)。

CMOSインバーターはpMOS・nMOSいずれもスイッチング可能な抵抗を用いた構造です。

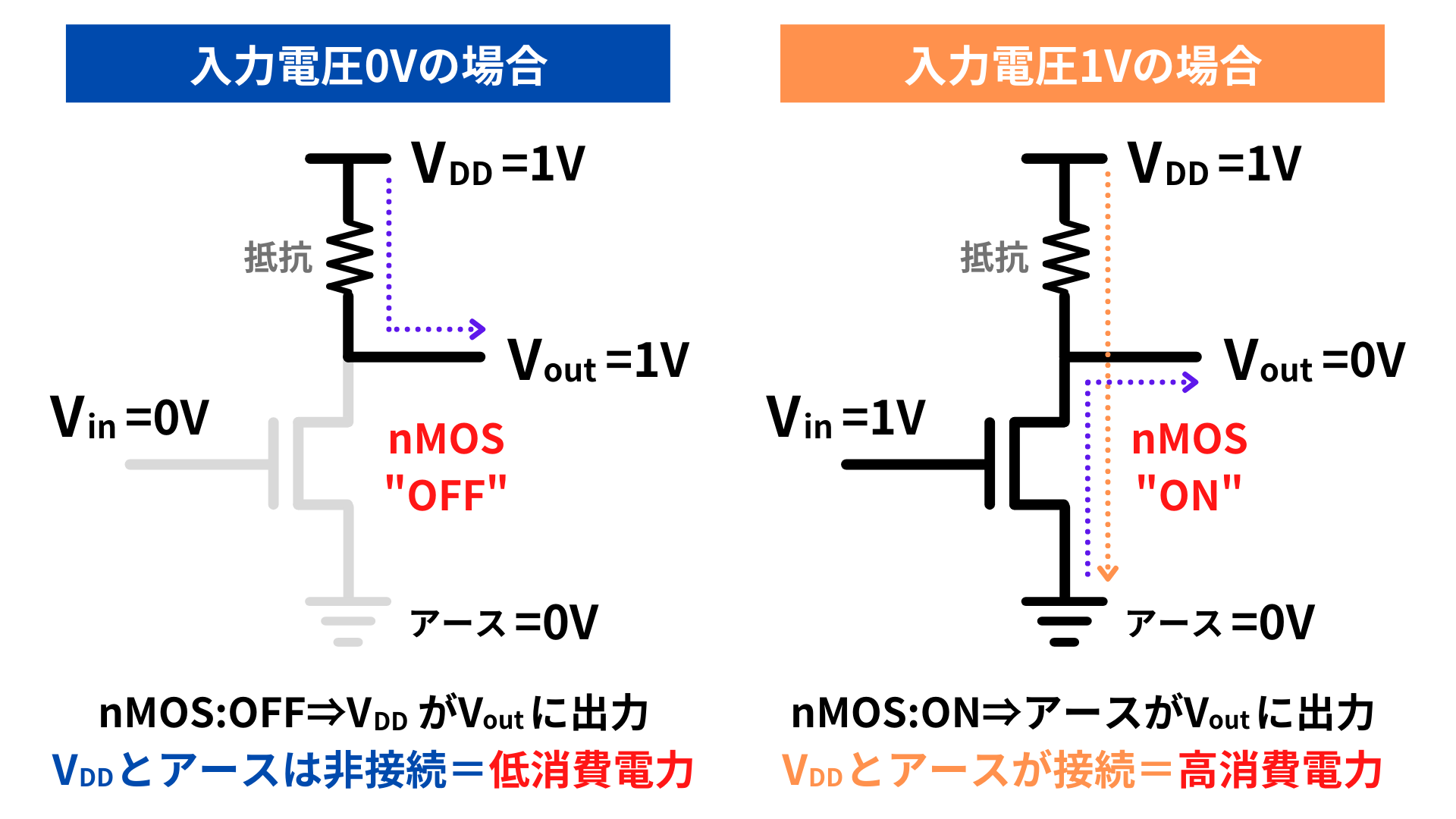

NMOSインバーターの動作原理

NMOSインバーターの動作は以下の通りです。簡略化のため、電源電圧を1V、接地を0Vとして考えてみましょう。

- Vin=0Vの場合

- Vin=1Vの場合

入力が0のとき、nMOSFETのゲートには電圧が印加されないためOFFになります。一方、pMOSFETはONとなり、出力(Vout)は電源(VDD)と接続されて1Vが出力されます。

このとき、VDDとアース間に電流は流れないため、消費電力はほとんどありません。

nMOSFETのゲートに正の電圧が印加されると、nMOSFETがONになり、出力(Vout)はアースと接続されて0Vが出力されます。

このとき、VDDとアースが接続されてリーク電流が流れるため、消費電力が増加します。

NMOSインバーターの場合、NMOSがONの状態で電源からアースに電流が流れ続けることになるため、消費電力が大きくなります。

PMOSインバーターも全く同じ原理で、pMOSがONの状態では電源からアースに電流が流れ続け、消費電力が増大します。

CMOSインバーターの動作原理

次に、CMOSインバーターの動作原理を見ていきましょう。

- Vin=0Vの場合

- Vin=1Vの場合

pMOSFETのゲートに負の電圧が印加されると、pMOSFETがONになります。一方、nMOSFETのゲートには電圧が印加されないため、nMOSFETはOFFです。

その結果、Voutは電源VDDと接続され、1Vが出力されます。VDDとアースは接続されないため、電流は流れず、消費電力は低くなります。

nMOSFETのゲートに正の電圧が印加されると、nMOSFETがONになります。pMOSFETのゲートには電圧が印加されないため、pMOSFETはOFFです。

その結果、Voutはアースと接続され、0Vが出力されます。VDDとアースは接続されないため、電流は流れず、消費電力は低くなります。

CMOSは、0の出力・1の出力いずれにおいても、電源とアースは接続されません。そのため、リーク電流が流れず常に消費電力が小さいのです。