MOSFETとは:構造・動作原理・応用

MOSFETの構造

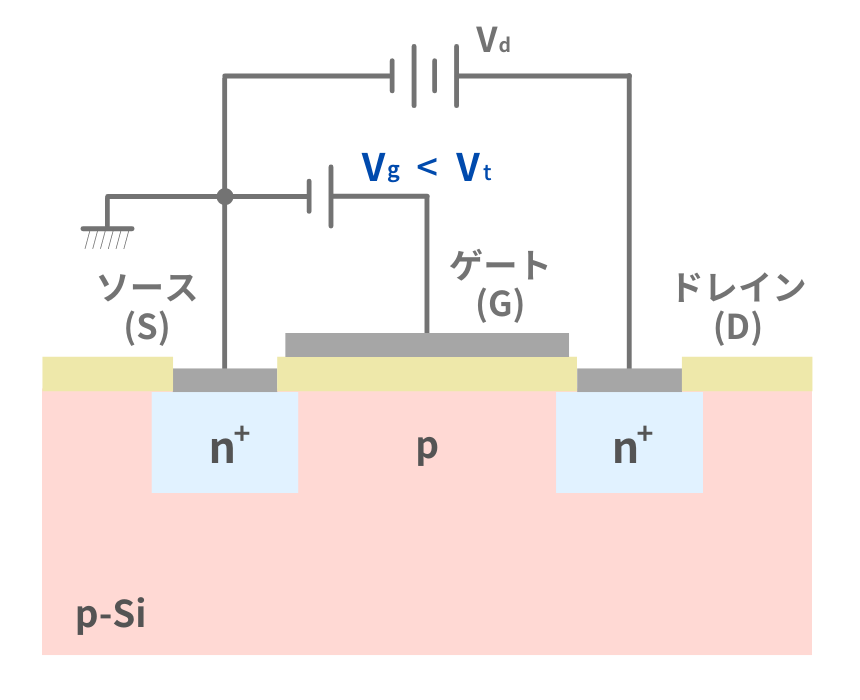

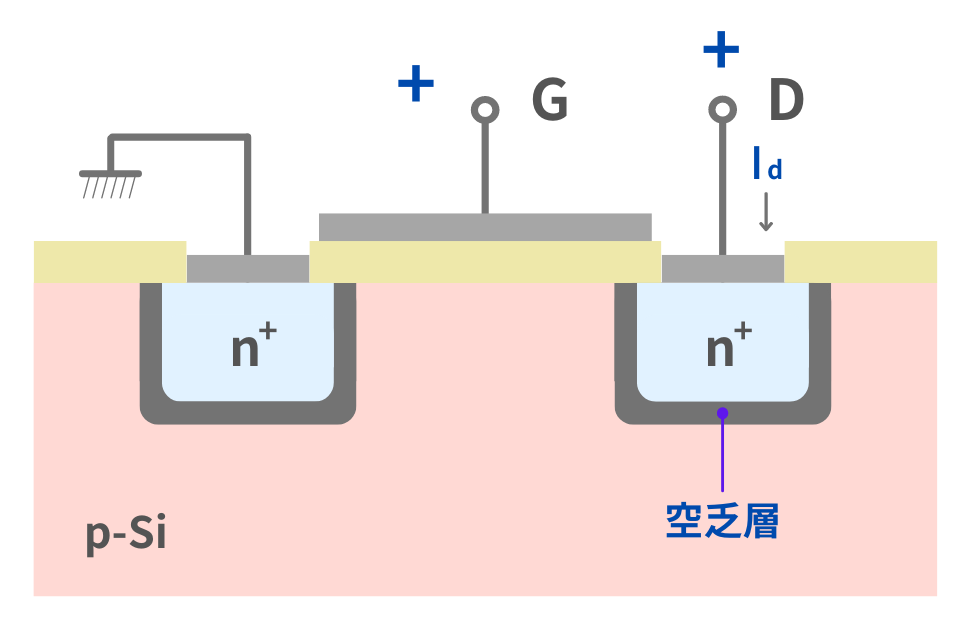

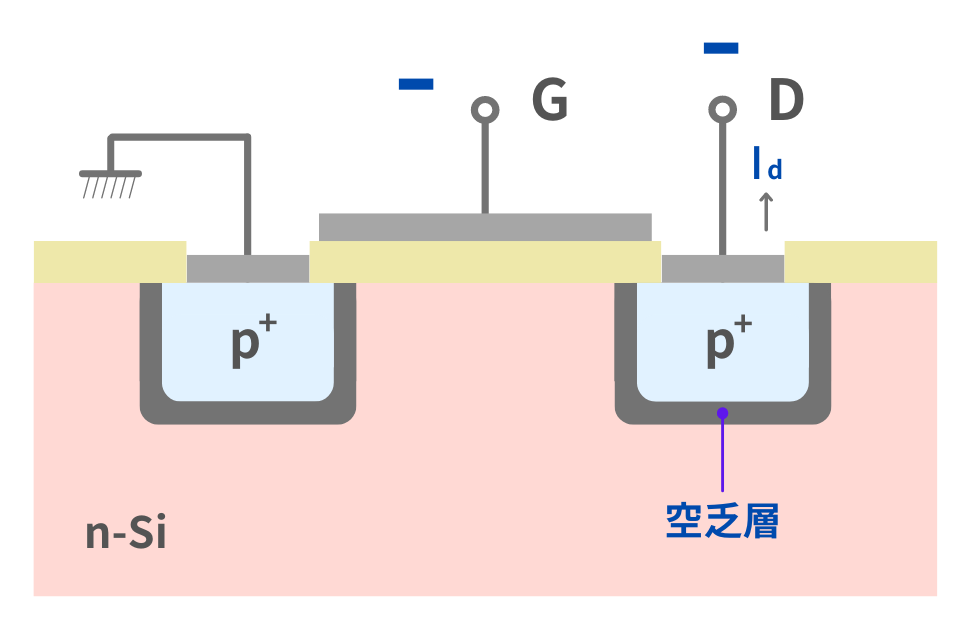

下図はnチャネル型MOSFETの構造です。

MOSFET(Metal-Oxide-Semiconductor Field Effect Transistor)は「ゲート電圧によって半導体表面(酸化膜界面)の電位状態を制御し、電流の通り道を形成・遮断するトランジスタ構造」です。半導体デバイスにおいて基本的な構造です。

MOSFETは、Si基板上に薄い酸化膜(ゲート絶縁膜)を介して金属電極を設けたMOSキャパシタ構造を基本とし、その両側にキャリアの供給源となるソース(S)領域とドレイン(D)領域が形成されています。

ソースおよびドレイン領域は、電流を効率よく流すために高濃度に不純物を添加(ドーピング)されています。

絶縁膜上に形成されたゲート(G)電極は、ゲートから電流を流し込むための電極ではなく、ゲート電圧によって半導体表面の電位を制御する役割を持ちます。この電位制御によって、ソースとドレインの間に電流が流れるかどうかが決まります(=トランジスタの基本)。

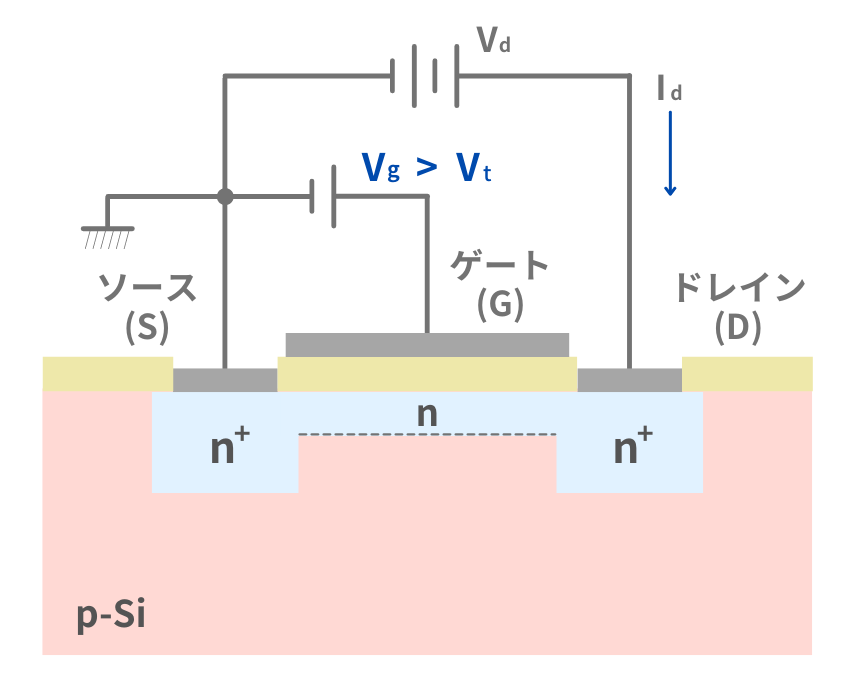

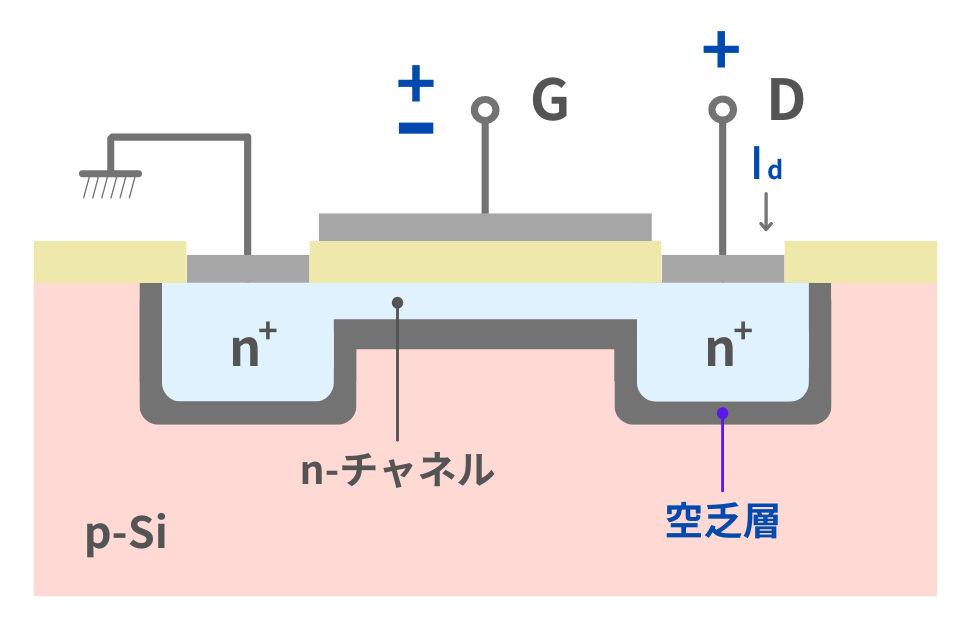

ゲート直下で電流が流れる領域をチャネルと呼びます。チャネル内を電子が流れるものをnチャネル型、正孔が流れるものをpチャネル型MOSFETと呼びます。チャネルは常に存在するわけではなく、ゲート電圧によって半導体表面に形成される領域です。

動作原理

n型とp型の違いは、チャネルを流れるキャリア(電子・正孔)の違いだけです。ここではnチャネル型MOSFETを例に、ゲート電圧によって電流の通り道がどのように変化するかを説明します。

ゲート電圧Vg < しきい値電圧Vt

(OFF状態)

ゲート電圧がしきい値電圧より低い場合、ソースとドレインをつなぐ電流の通り道(チャネル)は形成されません。

ソース-ドレイン間はpn接合によって分離され、電流は流れません(n-p-n構造。pn接合の逆バイアス状態)。

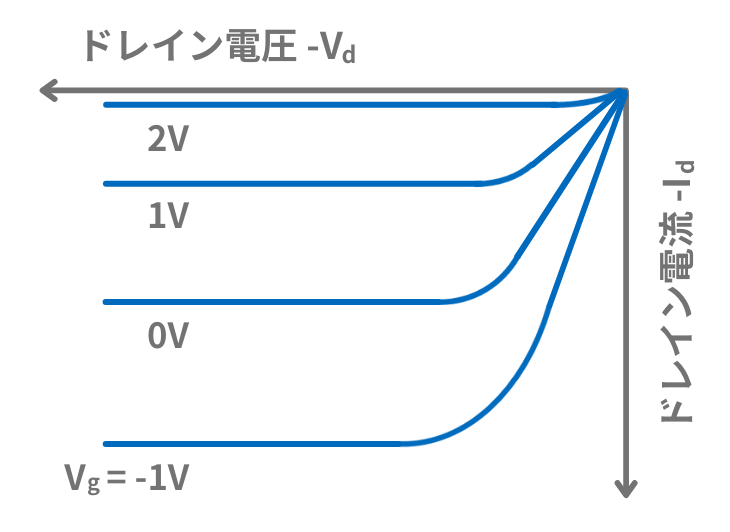

電流-電圧特性(I-V特性)

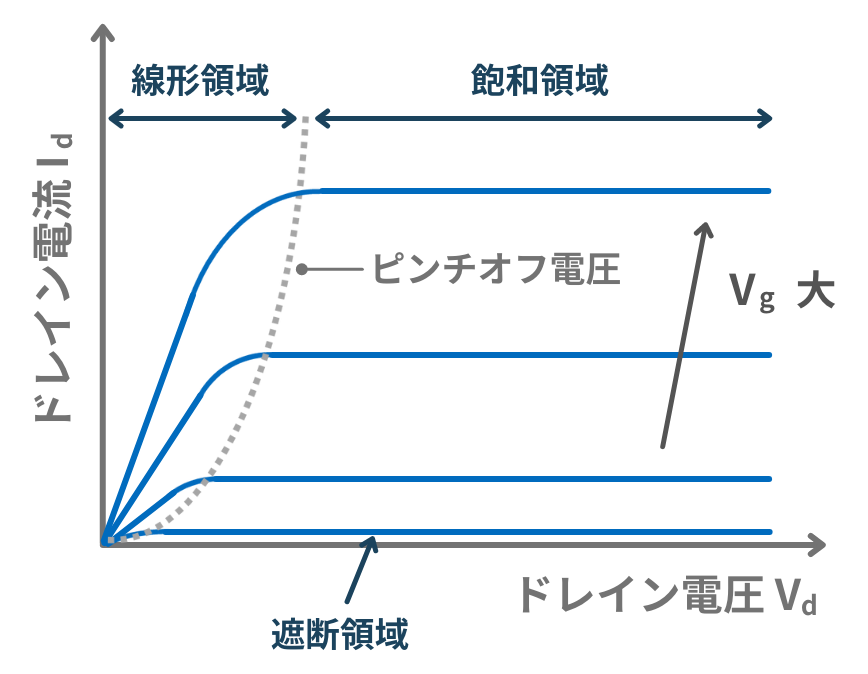

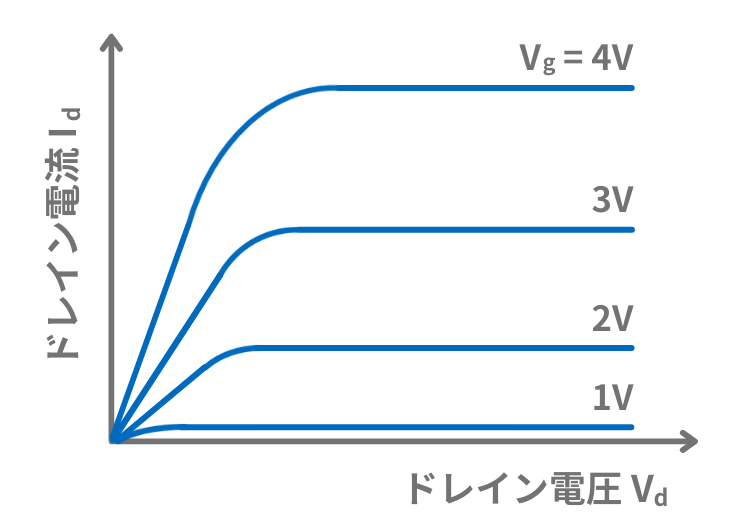

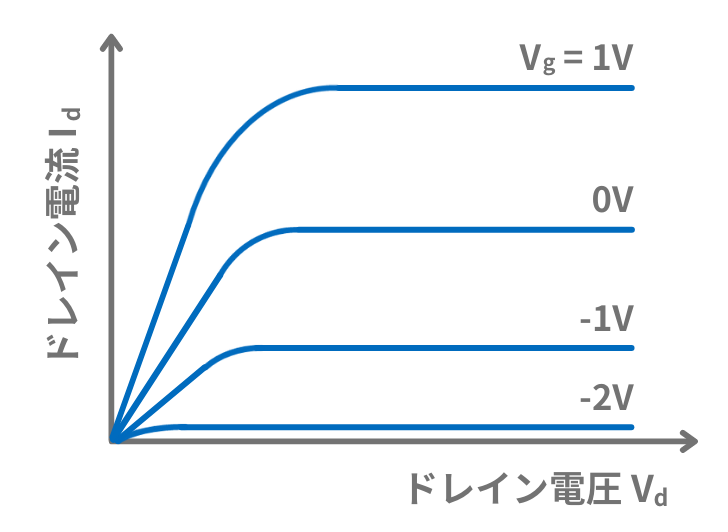

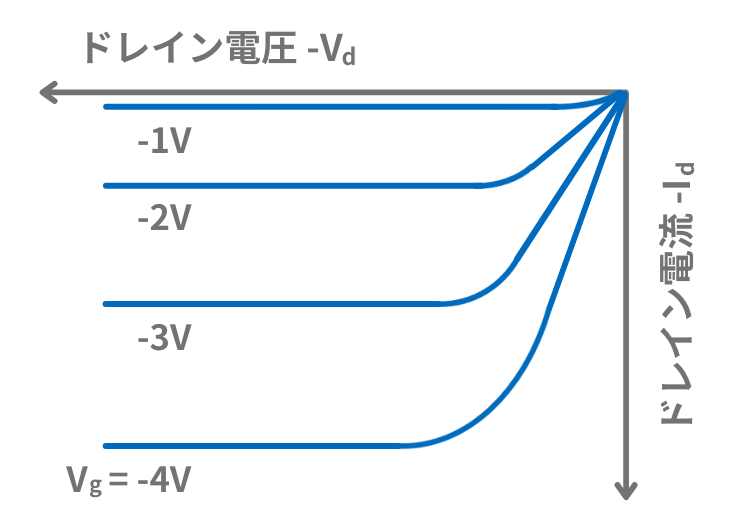

下図はMOSFETの電流-電圧特性です。

ゲート電圧を高くするとドレイン電流が増加し、またドレイン電圧を上げると電流も増加します。ただし、あるドレイン電圧を超えると、電流はそれ以上ほとんど増えなくなるという特徴があります。

このようなMOSFETのI-V特性は、以下の3つの領域に分けられます。

- 遮断領域

- 線形領域

- 飽和領域

ドレイン電圧Vdを印加してもドレイン電流Idが流れない領域。半導体表面にチャネルが形成されておらず、ドレイン電流はほとんど流れない。

ドレイン電圧Vdに比例してドレイン電流Idが変化する領域。チャネルが形成されている状態で、電流が流れる。チャネルは抵抗素子のように振舞い、電圧に比例して電流が増大するため、線形領域(直線領域)と呼ばれる。

ドレイン電圧Vdによらずドレイン電流Idが一定となる領域。ドレイン電圧増加によるドレイン近傍の空乏層生成により、チャネルが消滅するために発生する。

ドレイン電圧によりチャネルが消滅することを「ピンチオフ」と呼び、ピンチオフが起こる電圧をピンチオフ電圧と呼びます。

飽和領域において、ドレイン電圧を増加してもドレイン電流が一定値となるのはピンチオフが起こるためです。

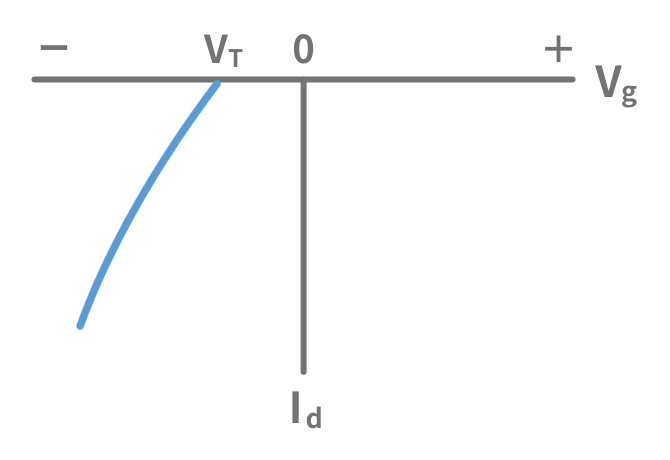

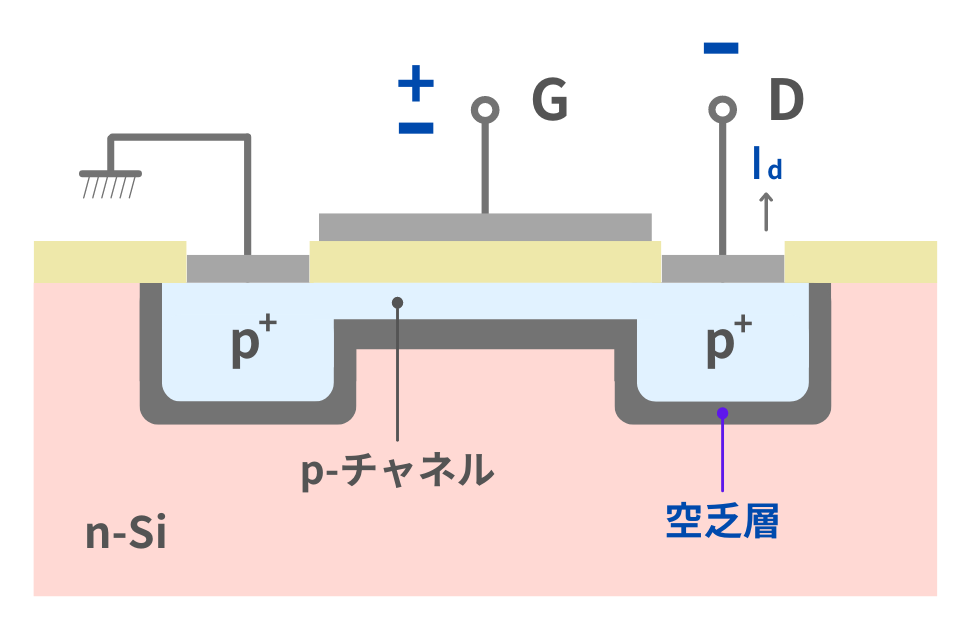

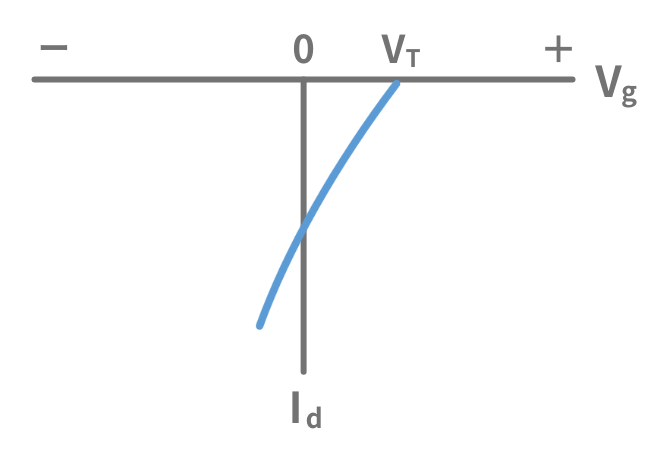

エンハンスメント型とディプレッション型

MOSFETは4つの種類があります。

| 型 | 断面図 | 出力特性 | 伝達特性 |

|---|---|---|---|

| n-チャネル エンハンスメント (ノーマリ・オフ) |  |  |  |

| n-チャネル ディプレッション (ノーマリ・オン) |  |  |  |

| p-チャネル エンハンスメント (ノーマリ・オフ) |  |  |  |

| p-チャネル ディプレッション (ノーマリ・オン) |  |  |  |

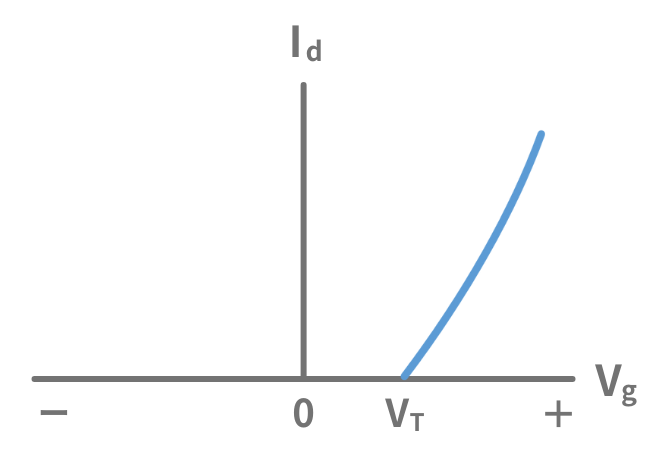

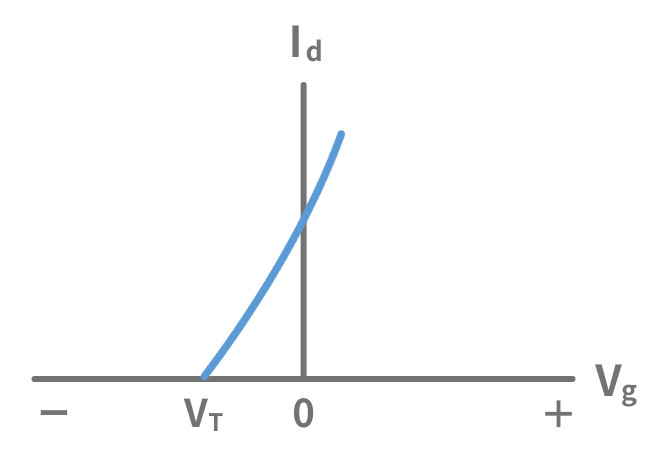

ゲート電圧がゼロの状態でチャネルが形成されないものをエンハンスメント型(ノーマリ・オフ)、ゲート電圧がゼロの状態でチャネルが形成されるものをディプレッション型(ノーマリ・オン)と呼びます。

チャネルの導電型(n型・p型)と合わせ、MOSFETは計4種類に細分化されます。

微細化とスケーリング則

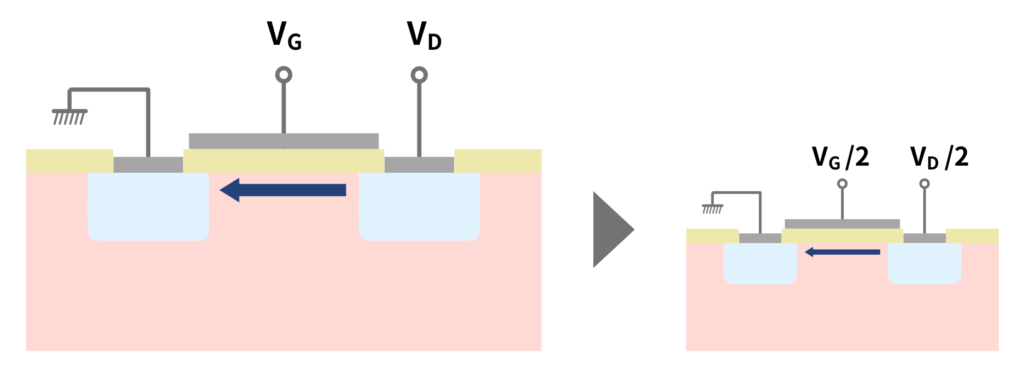

MOSFETは微細化するほど性能が向上する特徴があります。これは「スケーリング則(デナード則)」と呼ばれます。

MOSFETの大きさを1/k(k:スケーリング係数)とすると、MOSFET1個あたりの消費電力は1/k2に低下します。また、デバイス面積も1/k2となるためMOSFETの密度を大幅に増加させ、チップの高性能化が可能となります。

スケーリング則を技術的指針として、MOSFETは年々微細化し、性能が飛躍的に向上してきています。

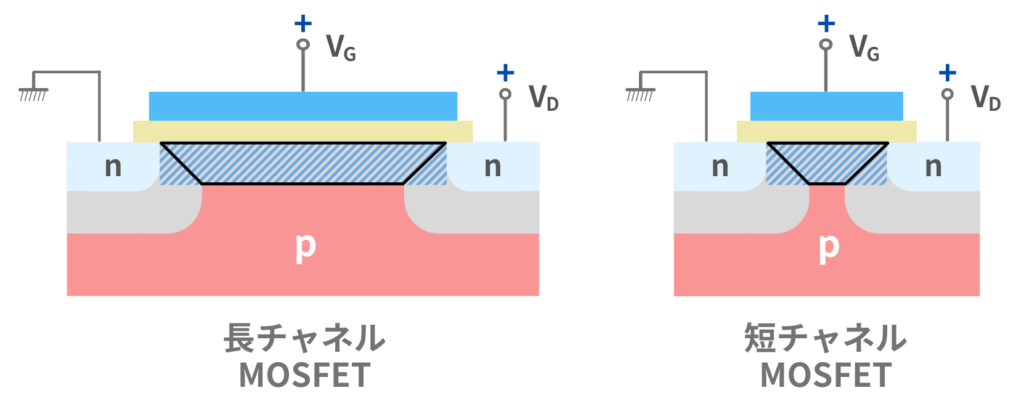

短チャネル効果

MOSFETでは微細化に伴いチャネル長さが減少すると、電気特性に悪影響が生じます。これを「短チャネル効果」と呼びます。

具体的に以下のような特性が現れます。

- しきい値電圧の低下

- ドレイン誘起障壁低下(DIBL)

- サブスレッショルド係数(S)の劣化

- 電流非飽和

- パンチスルー

チャネル長が短くなると、チャネルの反転層制御にゲート電圧のみならずドレイン電圧の影響も受けやすくなるため、静電制御性が低下します。

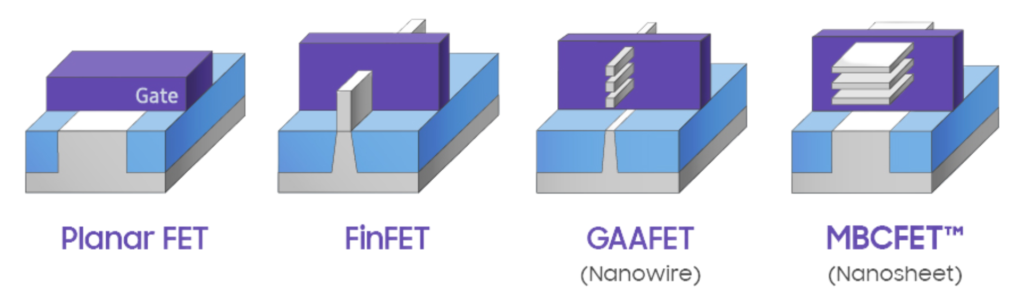

構造の変遷

説明では平面構造(プレーナー)のMOSFETを用いてきましたが、スマホなどの先端デバイス向けでは3次元的な構造のMOSFETが形成されています。構造の大まかな変遷を下図に示します。

先端デバイス用のMOSFETは、チャネルの複数方向をゲートで囲うFinFET(フィンフェット)やGAA(ゲートオールアラウンド)構造を採用し、性能向上を図っています。

例えば、ソース/ドレイン領域をFin状に形成したFinFETでは、チャネルの3方向がゲートで囲われた状態となります。従来のプレーナー構造よりもゲート電圧による静電制御性が高く、高速でのスイッチングが可能です。

最先端のMOSFETでは、チャネルとゲートの接触面積を増加することで、高性能化を図っています。

- MOSFET(Wikipedia)

- 閾値電圧(Wikipedia)

- トランジスタの構造と基本特性(2)(日本電気技術者協会)

- デバイスのスケーリング則(立命館大学)

- MOSFET(山形大学)

- 微細デバイスの諸問題(電子情報通信学会)

- Lecture #27(UC Berkeley)

- ドレイン誘起障壁低下(Wikipedia)

- デバイスのスケーリング則(立命館大学)

- サブスレッショルド伝導(Wikipedia)

- リーク電流(Wikipedia)

- チャネル長変調(Wikipedia)

- MOSFET(PC watch)

- Samsung,3nmプロセスで独自のGAAFET構造「MBCFET」採用へ(PC watch)

- FinFET(Wikipedia)

\専門家厳選!/

半導体学習に役立つ参考書・サイト