短チャネル効果とは:MOSFET微細化の限界と対策

短チャネル効果とは

短チャネル効果とは「MOSFETの微細化に伴い、チャネル長が短くなることにより現れる、静電特性への影響(の総称)」です。

短チャネル効果が発生すると、MOSFETの消費電力が増加したり、特性のばらつきが大きくなるなど悪影響が生じるため問題です。

短チャネル効果の具体例として以下があります。

- しきい値電圧の低下

- ドレイン誘起障壁低下(DIBL)

- サブスレッショルド係数(S)の劣化

- 電流非飽和

- パンチスルー

1つずつ解説していきます。

しきい値電圧の低下

しきい値電圧の低下とは「短チャネルMOSFETにおいて、ドレイン電圧VDが大きい場合にしきい値電圧VTが低下する現象」です。

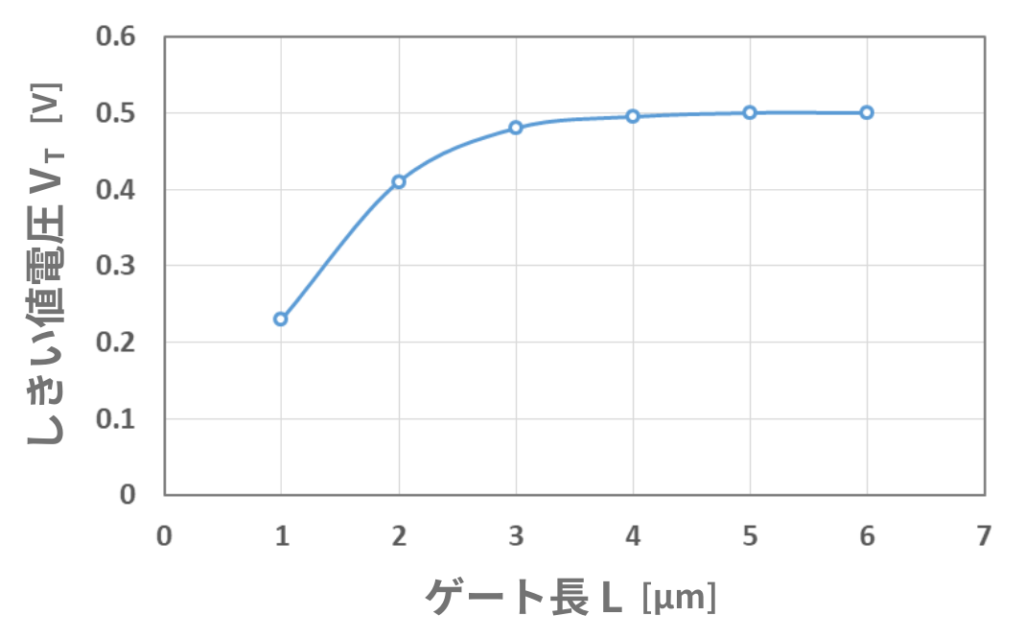

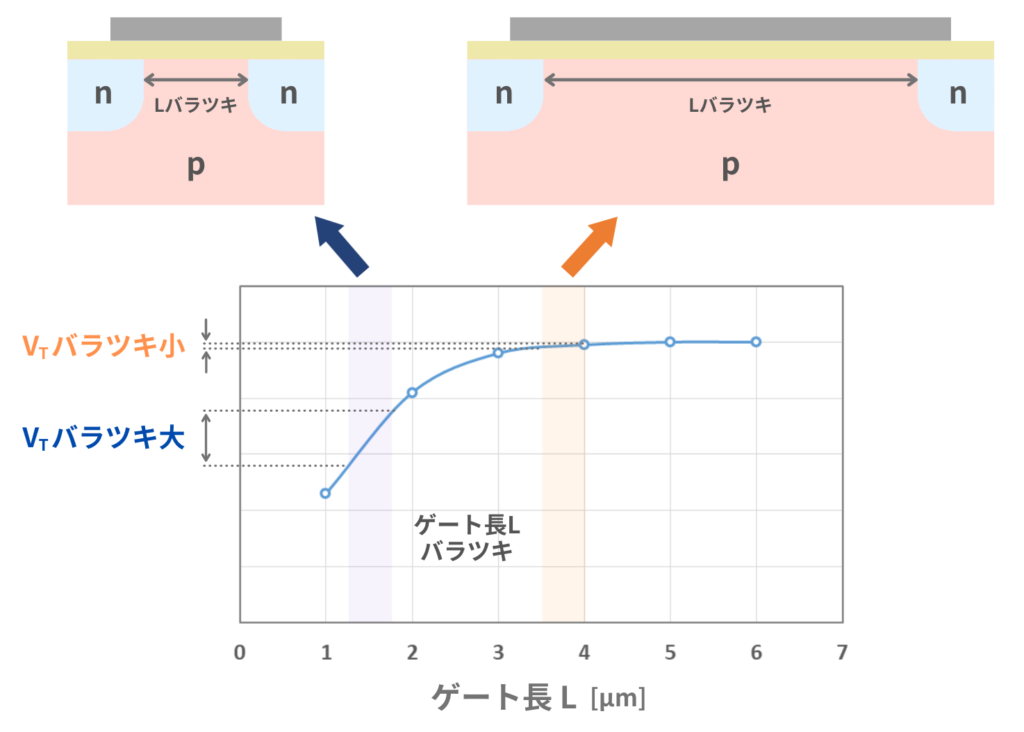

言い換えると、しきい値電圧がゲート長に依存して変化します。ゲート長さが短い「短チャネル領域」で急激にしきい値電圧が低下します。

短チャネル領域でのしきい値電圧低下は、最先端のMOSFETにおいて致命的な問題を引き起こします。

しきい値電圧低下の問題点

しきい値電圧低下は「チャネル長のバラツキにより大きくしきい値が変化し、デバイス工程の歩留まりを低下させるため問題」になります。

MOS集積回路の製造工程において、プロセス上のバラツキを排除することは出来ず、ゲート長もばらつくことが知られています。

長チャネルMOSFETではゲート長がある範囲をもってバラついても、しきい値電圧の変化量は小さく、問題となりません。

一方、短チャネルMOSFETでは、チャネル長がバラつくとしきい値電圧も大きく変化してしまいます。しきい値電圧のバラツキはデバイス設計で問題となるため不良品です。すなわち、MOSFETの歩留まりを低下させます。

しきい値電圧低下の原理

しきい値電圧低下は「ソース・ドレイン電圧がチャネル内の電荷の誘起に寄与するため発生」します。

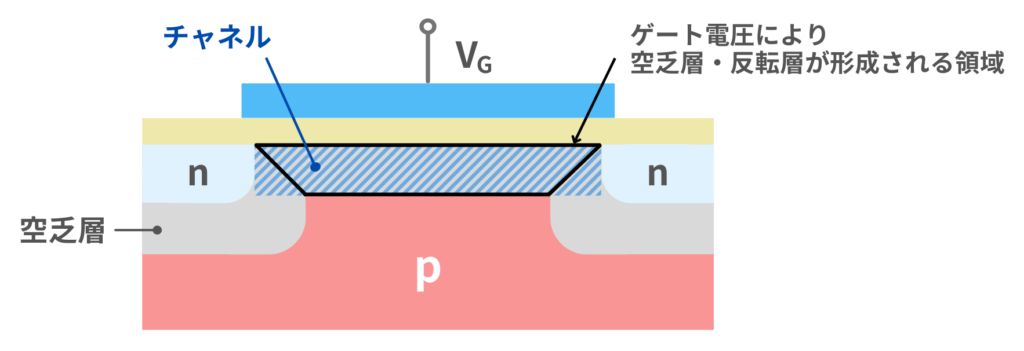

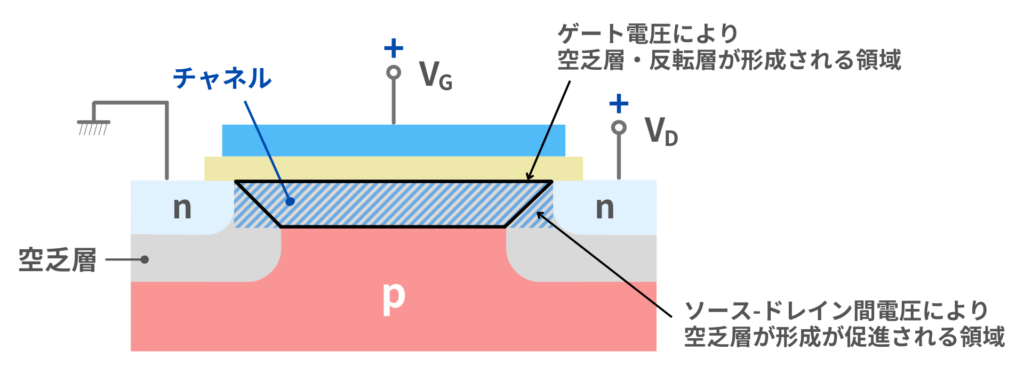

上図はMOSFETのチャネル近傍の拡大図です。斜線部はチャネル部を表しています。MOSFETのON状態とは、ゲート電圧によりチャネルに反転層が形成され、ソース-ドレイン間に電流が流れることを指します。

ゲート直下のチャネルへの反転層形成は、主にゲート電圧により制御されます。しかし実際には、ソース-ドレイン電圧によっても反転層の形成が誘起されます

下図は、ゲート電圧とドレインに正電圧を印加した場合のチャネル近傍拡大図です。

上図は、ゲート電圧とドレインに正電圧を印加した場合のチャネル近傍拡大図です。ゲート正電圧による反転層形成促進に加え、ドレインの正電圧によっても反転層形成が誘起されます。すなわち、反転層形成に必要なしきい値電圧はゲート電圧分低下します。

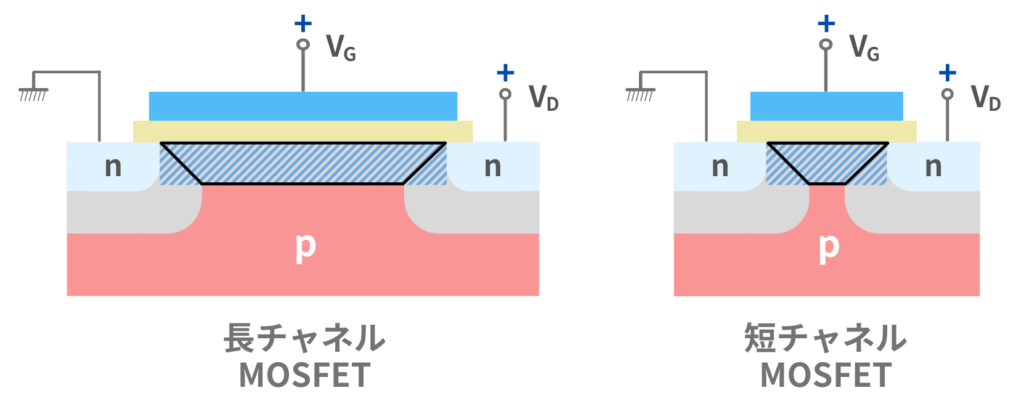

下図は長チャネルMOSFETと短チャネルMOSFETの比較です。

長チャネルMOSFETの場合、チャネル領域と比較し、ドレイン電圧で反転層形成が誘起される領域はわずかです。つまり、ドレイン電圧によるしきい値電圧低下はわずかです。

短チャネルMOSFETの場合、ドレイン電圧で反転層が誘起される領域の割合が増加するため、しきい値電圧の低下割合が増加します。これが短チャネルMOSFETでしきい値電圧低下する原理です。

ドレイン誘起障壁低下(DIBL)

ドレイン誘起障壁低下(DIBL)とは「ドレイン電圧が大きい場合に、しきい電圧が低下する現象」です。

DIBLが発生すると、ID-VG特性が低電圧側にシフトするため、オフリーク電流が増加するため、消費電力が増大する問題を生じます。

DIBLの原理

DIBLは、しきい値電圧低下と同じ原理で説明されます。

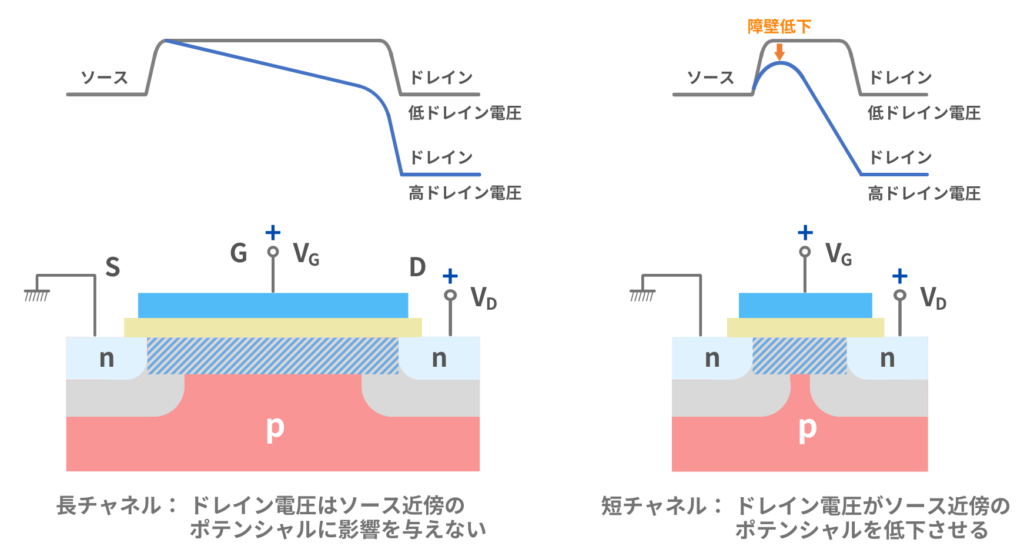

DIBLは「ドレイン電圧がソース近傍のポテンシャルを低下させるため」発生します。

前述の通り、ドレイン電圧もチャネルの反転層形成(=ポテンシャル低下)に寄与します。例えば、ゲート電圧およびドレインに正の電圧を印加した場合、ドレイン電圧はドレイン近傍の反転層形成を誘起します。

すなわち、ドレイン近傍での電子のポテンシャルエネルギーが低下します。長チャネルMOSFETの場合、ドレイン電圧によるポテンシャル低下はドレイン近傍のみであり、ソース近傍のエネルギー障壁高さには影響を与えません。

短チャネルMOSFETの場合、ソース-ドレイン距離が近く、ドレイン電圧はソース近傍のポテンシャルまで低下させます。これがDIBLの原理です。

ソース・ドレイン近傍のポテンシャル障壁が低下するとソース・ドレイン間の漏れ電流も大きくなるため、問題です。

サブスレッショルド係数(S)の劣化

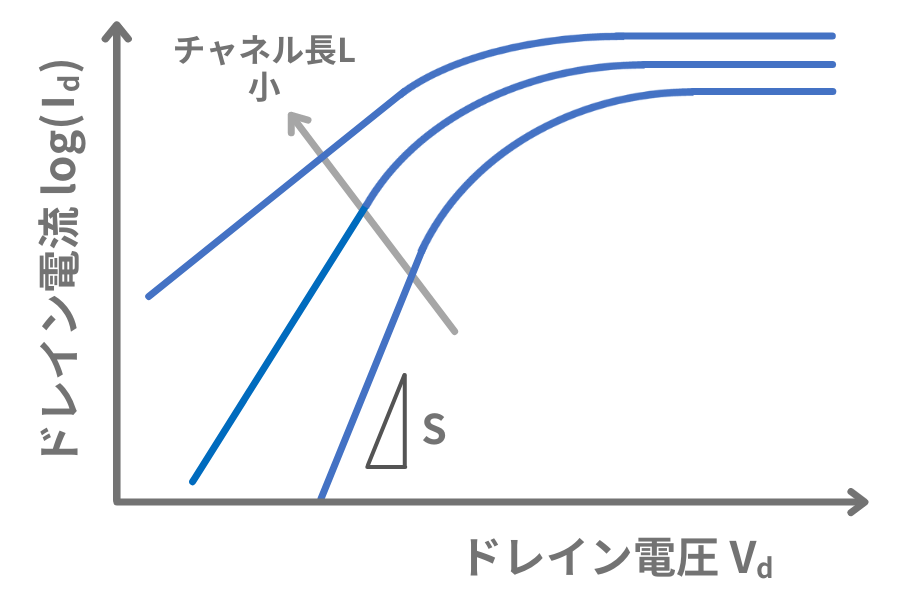

チャネル長が短くなると「サブスレッショルド係数(S)が劣化」します。

サブスレッショルド係数とは「ゲート電圧がしきい値以下の弱い反転領域(=サブスレッショルドルド領域)において、電流値が1桁するために必要なゲート電圧増加量」です。

サブスレッショルド係数(S)が大きい場合、ゲート電圧変化に対する電流値変化が小さくなるため、MOSFETのスイッチング特性が悪化します。スイッチング特性の悪化は、リーク電流増加引き起こし、デバイスの消費電力を増加させるため問題です。

サブスレッショルド係数劣化の原理

DIBLで説明した通り、短チャネルMOSFETの場合、ソース-ドレイン距離が近く、ドレイン電圧はソース近傍のポテンシャルまで低下させます(nチャネルMOSFETの場合、ドレイン電圧によりソース近傍の電子が引き抜かれる)。

短チャネルMOSFETではドレイン電圧がチャネルの反転層形成に寄与するため、ゲート電圧によるドレイン電流制御性が弱く、サブスレッショルド係数が劣化するのです。

電流非飽和

短チャネルMOSFETでは「ピンチオフ電圧以上の飽和領域で電流が飽和しない現象」が発生します。

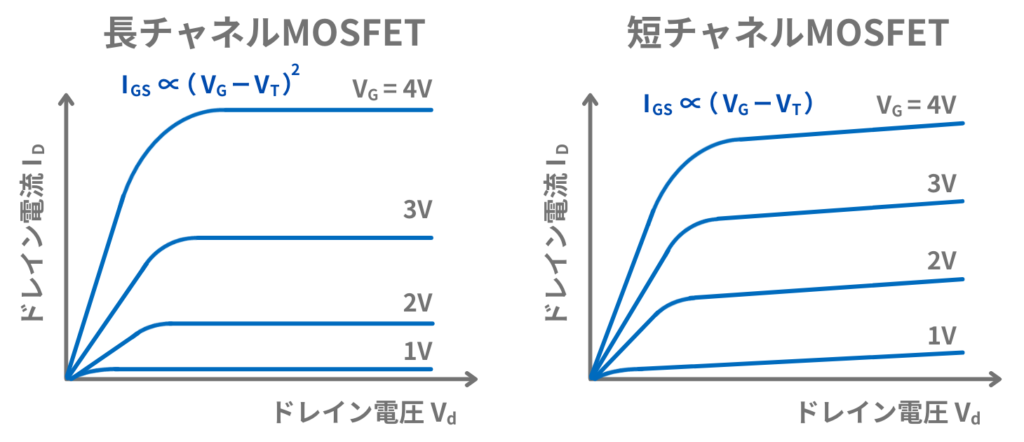

長チャネルMOSFETではピンチオフ電圧以上のドレイン電流を印加しても、電流値は一定となります。しかし、短チャネルMOSFETでは飽和領域においてもドレイン電圧と共にドレイン電流が漸増します。

また、長チャネルMOSFETではドレイン電流IDが(VG-VT)2に比例するのに対し、短いチャネルMOSFETでは(VG-VT)に比例します

電流非飽和の原理

短チャネルMOSFETの飽和領域において電流値が非飽和となるのは様々な要因の結果ですが、以下の2点が主な理由です。

- ドレイン電圧によるしきい値電圧の減少(DIBL)

- チャネル長変調効果

DIBLによる電流非飽和

DIBLで説明した通り、短チャネルMOSFETの場合、ドレイン電圧の増加に伴って閾値電圧VTが低下します。

つまり、ドレイン電圧が増加するほど反転層のキャリア濃度が増大し、飽和領域のドレイン電流もVDに伴って増加します。

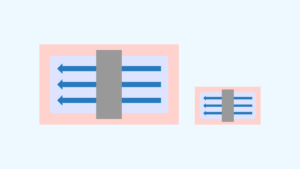

チャネル長変調効果

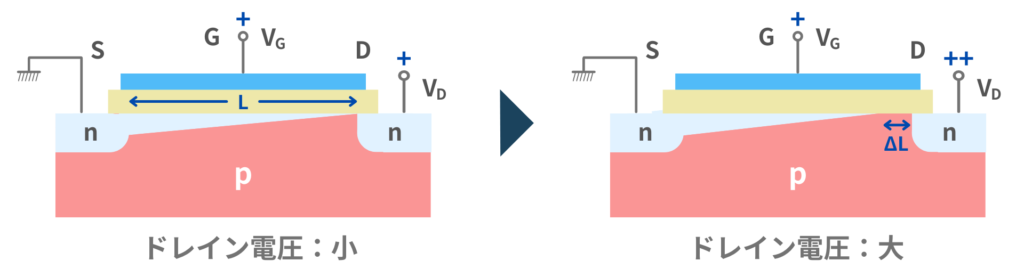

チャネル長変調効果とは「ドレイン電圧が大きい場合、ドレイン電圧が増加すると反転チャネル領域の長さが短くなる現象」です。

MOSFETにおいてドレイン電圧を増加すると、ドレイン近傍の空乏層厚さが増加しドレイン近傍のチャネル(反転層)が消滅します(ピンチオフ)。

ドレインの空乏層が広がるとチャネル領域が短くなります。抵抗は長さに比例するため、チャネルが短くなると抵抗が減少します。すなわち、ドレイン電圧を増加するとチャネルの抵抗が下がり、ドレイン電流が増加します。これがチャネル長変調効果です。

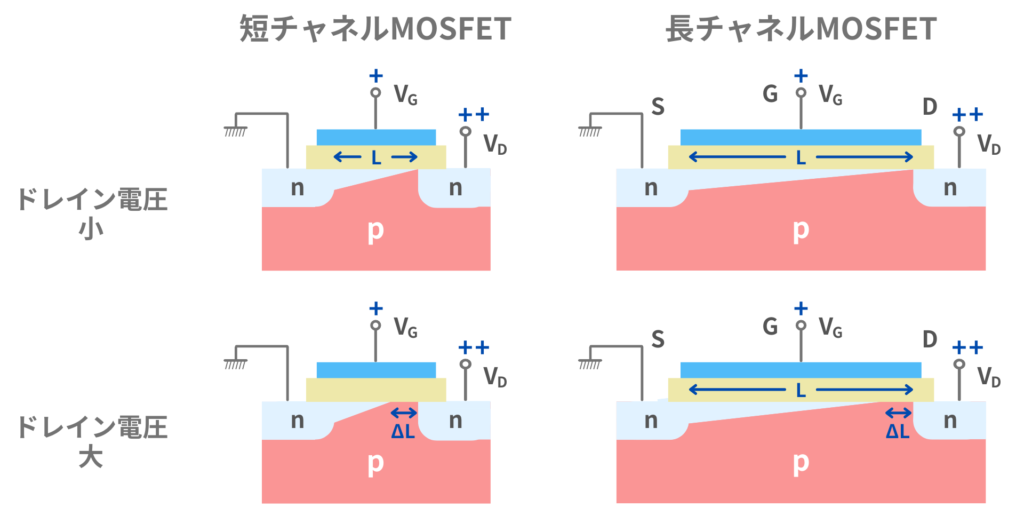

下図は長チャネルと短チャネルMOSFETの模式図です。チャネル長変調効果はチャネル長が短くなるほど顕著になります。

ピンチオフ時のチャネル長さをL、チャネル長変調によるピンチオフ点の移動距離をΔLとします。ΔLが同じ場合、元のチャネル長に対するチャネル長さの減少割合=ΔL/Lは、短チャネルMOSFETの方が大きくなることが分かります。

ドレイン電圧増加によるチャネル長の変化割合が大きいということは、チャネルの抵抗変化も大きいことを意味します。すなわち、短チャネルMOSFETほどドレイン電圧増加によるドレイン電流増加量が大きくなります。

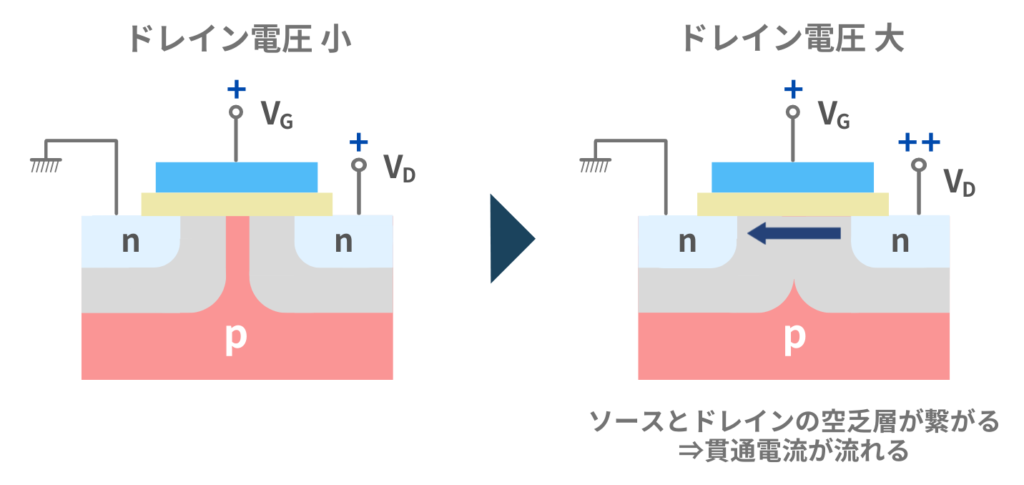

パンチスルー

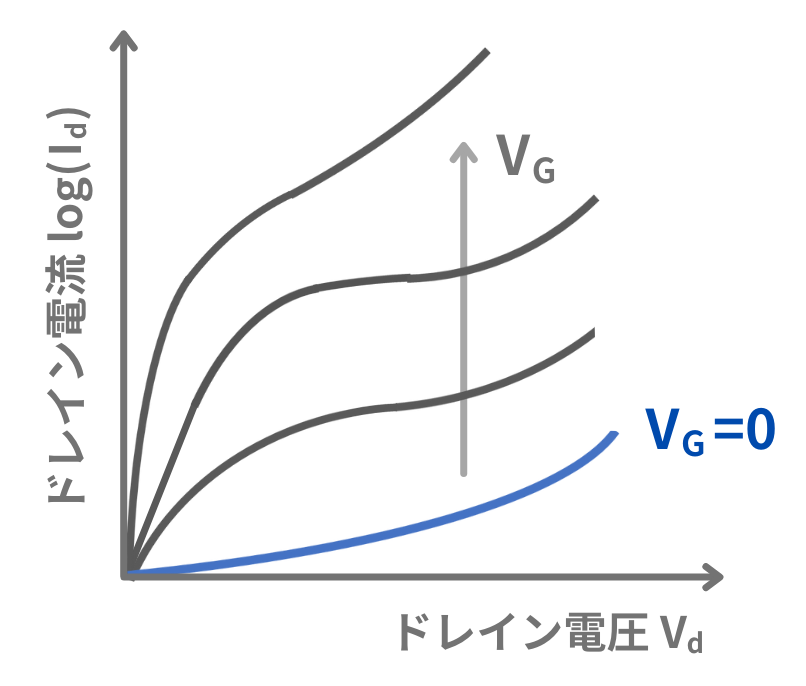

パンチスルーとは「ゲート電圧を印加していないにも関わらず、ソース-ドレイン間に貫通電流が流れる現象」です。

ゲート電圧VG=0でもドレイン電流が生じるため、トランジスタとして機能せず、消費電力も増加してしまうため問題です。

パンチスルーの原理

パンチスルーはドレイン電圧増加によりドレインの空乏層が広がり、ドレイン空乏層とソース空乏層が繋がるため発生します。

ソースとドレイン空乏層が繋がると、ソース-ドレインが直接接続されたとみなされるため、電流が流れてしまうのです。

DIBLで説明した通り、ドレイン電圧がソース近傍のポテンシャルを押し下げ障壁が低下するため、電流が流れると言えます。

前の講座

次の講座