フラッシュメモリとは:構造と動作原理

本記事の内容の一部は、半導体メモリに詳しいエンジニア・東急三崎口さんにご協力いただきました。普段はこちらのブログで発信されています。

フラッシュメモリとは

フラッシュメモリは「電源を切ってもデータを保持し(不揮発性)、データを電気的に書き換え可能なの半導体メモリ」です。

不揮発性で大容量な特徴を生かし、様々なデジタル機器に使われています。例えば、

- スマートフォンのストレージ

- USBメモリ

- SDカード

- SSD(Solid State Drice)

これらはすべてフラッシュメモリです。

半導体メモリには電源を切るとデータが消えてしまうもの(揮発性)が多いですが、フラッシュメモリは電源を切ってもデータを保持することができます(不揮発性)。

CDや磁気ディスク(VHS・フロッピーなど)は、読み書きに光や磁気を使っていたのに対し、フラッシュメモリは電子回路だけで読み書きが可能です。可動部がなく小型・高速で、安定した記録媒体として広く普及しました。

フラッシュメモリの基本構造

フラッシュメモリはなぜデータを保持できるのかを学ぶため、デバイスの基本構造を見ていきましょう。

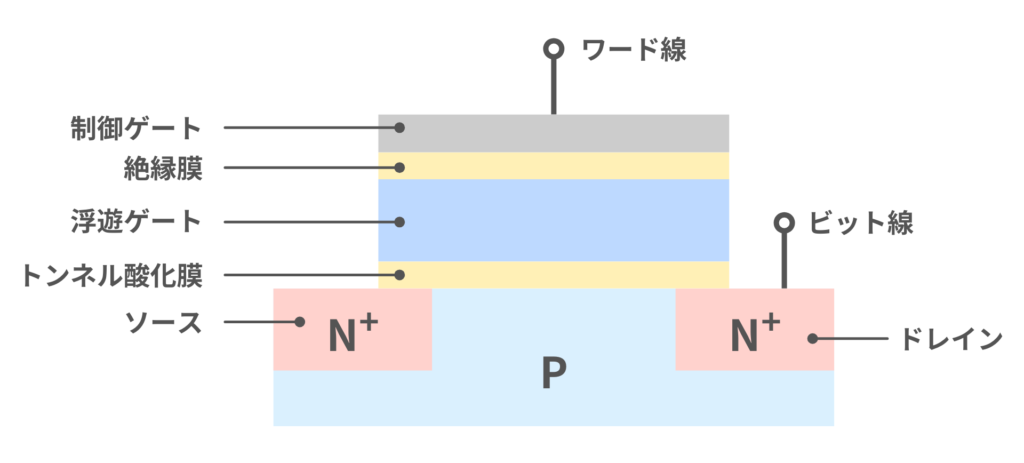

フラッシュメモリセルは、P型半導体基板にN+のソース・ドレインが設けられ、P型基板上にトンネル酸化膜・浮遊ゲート・絶縁膜・制御ゲートが積層した構造になっています。

- 浮遊ゲート(フローティングゲート)

- 制御ゲート

- トンネル酸化膜

- 絶縁膜

電荷を蓄積するゲート。電荷の有り・無しがメモリの0・1に対応します。フラッシュメモリでは、浮遊ゲートに電荷がない状態を1と認識します。

電圧を印加することで浮遊電荷を集める電極。

数nmの薄い酸化膜(絶縁膜)。薄いため、高電圧印加時に電流を通す(トンネル電流)。書き込み時に浮遊ゲートに電荷を蓄積する役割があります。

ゲート電極と浮遊ゲートを絶縁する酸化膜。

フラッシュメモリでは制御ゲートに電圧を印加し、浮遊ゲートに電荷を集め・保持します。浮遊ゲートは絶縁膜に挟まれているため、漏れ電流が小さいことから電源を切っても記憶が保持されます。

ゲート電圧印加による電荷の保持はMOSFETの動作原理が参考になります。

フラッシュメモリの動作原理

フラッシュメモリには、以下の3つの動作があります。

- 書き込み(0)

- 消去(1)

- 読み出し

それぞれの動作原理を解説します。

書き込み・消去

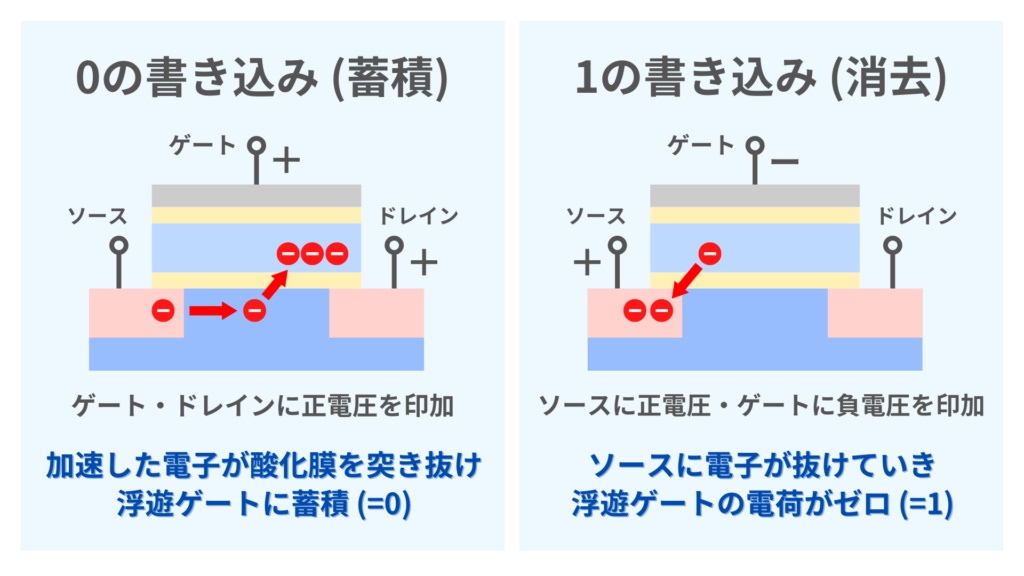

フラッシュメモリは、電荷を電気的に注入・引き抜くことで、データを書き込み・消去しています。

フラッシュメモリの「0」の書き込みは、浮遊ゲートに電荷を蓄積することに相当します。「1」の書き込みは浮遊ゲートの電荷を抜く動作であり「消去」に相当します。

- 0の書き込み=蓄積

- 1の書き込み=消去

制御ゲート・ドレインに正電圧を印加。ソース-ドレイン間に電子が流れ、加速された電子の一部が浮遊ゲートに蓄積

ソースに正電圧、制御ゲートに負電圧を印加。ソースに電子が引き抜かれ、浮遊ゲートの電荷が消去

読み出し

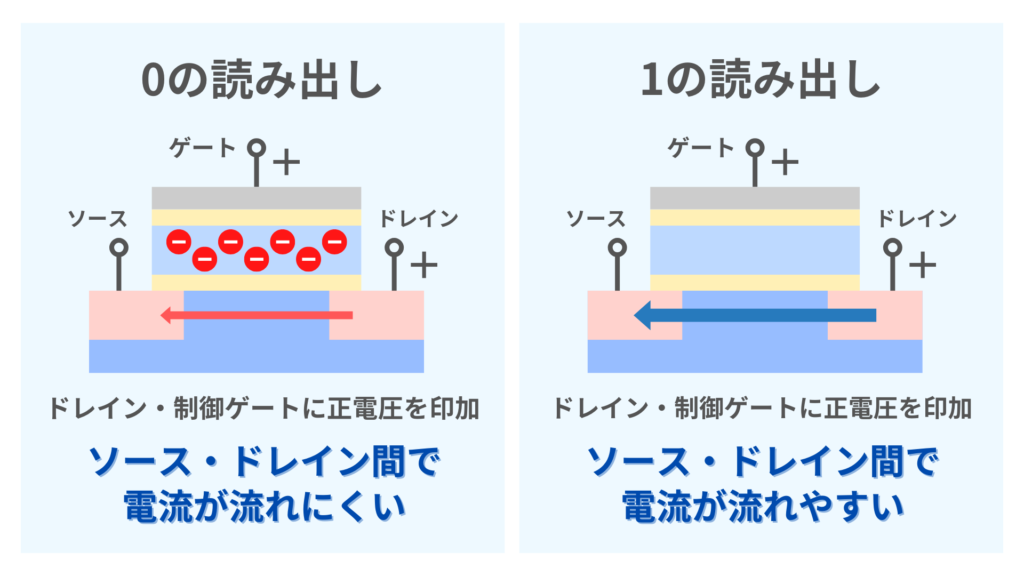

フラッシュメモリに保存されたデータを利用するには、0と1の情報を読み出す必要があります。

フラッシュメモリでは「制御ゲートに正電圧を印加し、ソース・ドレイン間電流の大きさによって「0」か「1」かを判断」します。浮遊ゲートに電荷が蓄積されている(=0)と電流は流れにくく、電荷がない(=1)と大きな電流が流れます。

- 0の読み出し

- 1の読み出し

制御ゲート・ドレインに正電圧を印加。フローティングゲートに蓄積された電子(負電荷)がチャネル形成を妨げるため、ソース-ドレイン間に流れる電流は小さい

制御ゲート・ドレインに正電圧を印加。ソース-ドレイン間に大きな電流が流れる

電荷の有無に応じたソースードレイン間電流の大きさから、電荷があるかどうかを判断し、データを読み取っています。

フラッシュメモリの種類:NAND型・NOR型

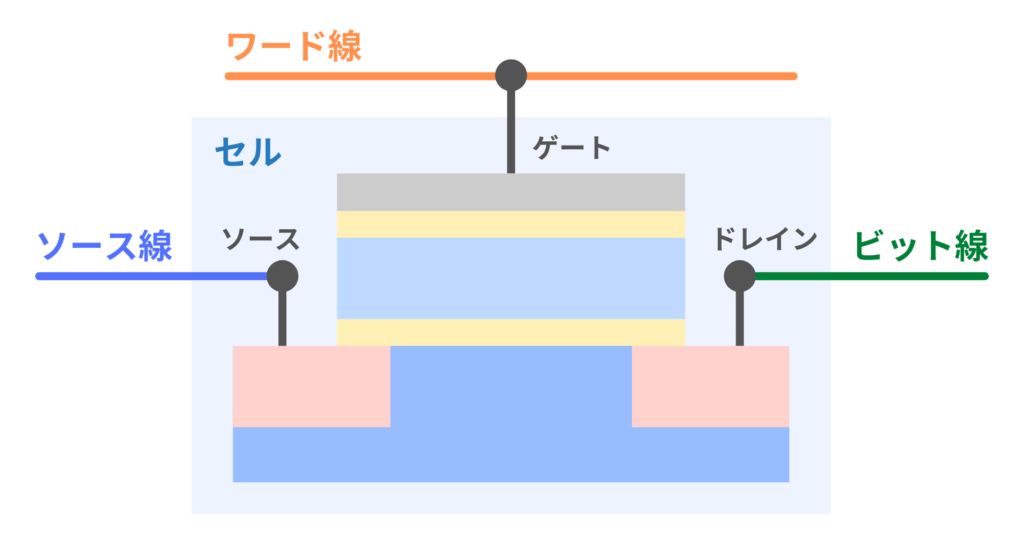

フラッシュメモリは「データを保管するメモリセル(フローティングゲート型トランジスタ)と、セル同士を制御・接続する3種類の配線(ワード線・ビット線・ソース線)」で構成されます。

| 配線名 | 対応端子 | 役割 |

|---|---|---|

| ワード線 | ゲート(制御ゲート) | ゲート電圧を印加して、セルの選択や制御を行う |

| ビット線 | ドレイン | 読み出し時の電流を取り出す線。データの「出入口」 |

| ソース線 | ソース | 書き込み・消去動作時に電位を制御する基準線 |

ワード線とビット線によって対象セルを選択し、読み書き動作に必要な電圧を印加することでデータをやり取りします。

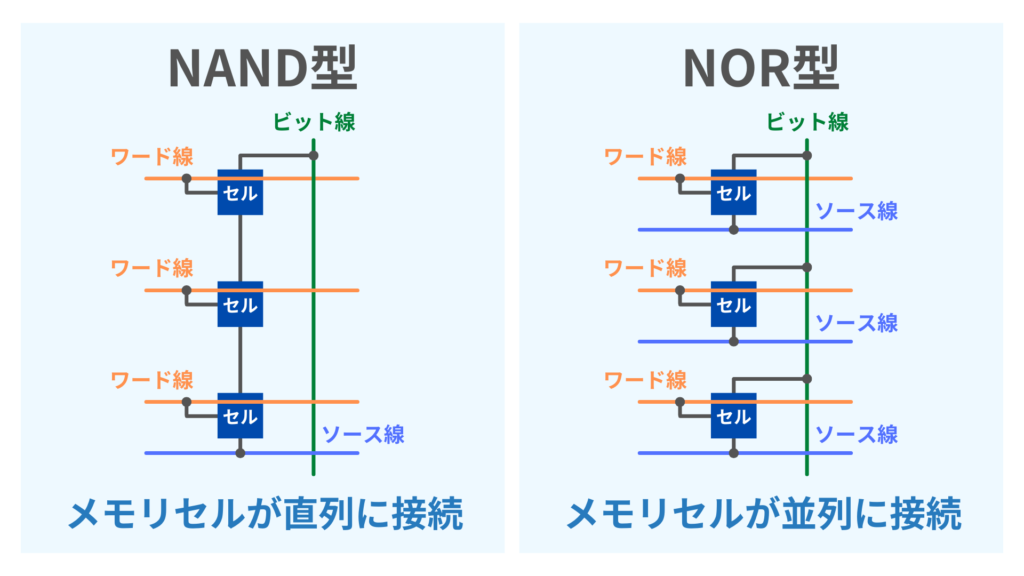

フラッシュメモリはメモリセルと配線の接続方式によりNAND型とNOR型に分けられます。

- NAND型フラッシュメモリ

- NOR型フラッシュメモリ

複数のセルを直列に接続し、ワード線・ビット線・ソース線を共有する構造。配線が簡素なため高集積・低コスト・大容量化に適しますが、アクセスはブロック単位となりランダムアクセスはできません。

各メモリセルが独立してビット線に接続され、必要なセルだけを直接選択できる構造。ランダムアクセスが可能なためコード実行に適しますが、配線が増えて集積度が低く、大容量化には不利です。

NAND型は、デジタルカメラ、スマートフォン、USBメモリ、SSDなど、安価・大容量が求められるストレージに広く利用されています。

一方、NOR型は、ルーター・プリンター・車載機器など、頻繁にコードを読み出すが書き換え頻度が低い、ファームウェア保存用途に適しています。

前の講座

次の講座