SRAMとは何か?構造と動作原理をわかりやすく解説

SRAMとは?

SRAM(Static Random Access Memory)は「データの読み出し/書き込みが可能なメモリ(RAM)の一種」です。MOSFETを用いたCMOSインバーター回路を組み合わせた構造をしています。

SRAMは、電源が入っている間だけデータを保持できる揮発性メモリです。DRAMと違って、データを維持するための定期的な読み書き(リフレッシュ)が必要ないのが特徴です。

SRAMの構造

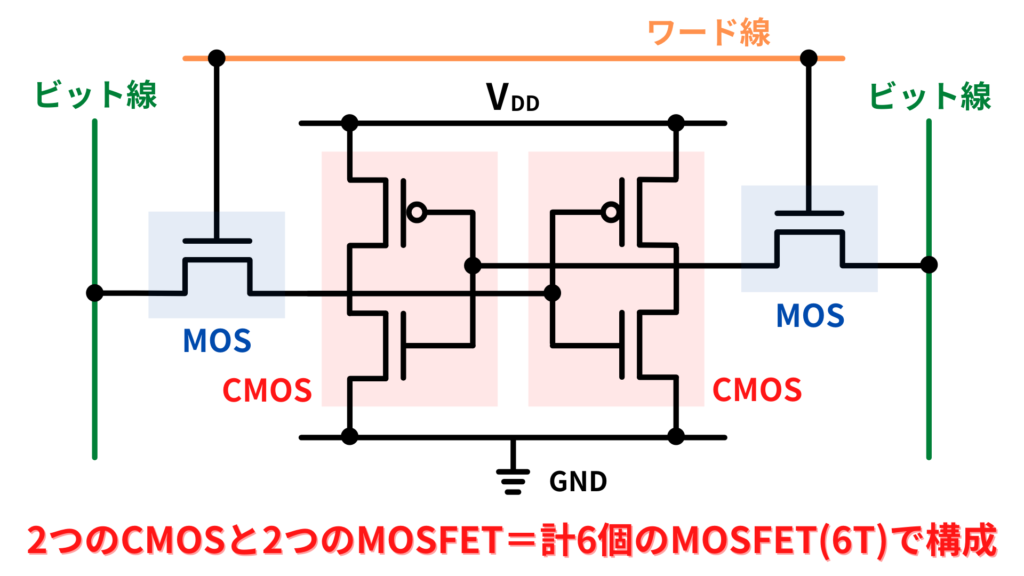

SRAMにも種類がありますが、最も基本的な構造は下記の6トランジスタセル(6T)です。

SRAM(Static Random Access Memory)は、2つのCMOSインバーターと2つのアクセス用MOSFETで構成される「6トランジスタセル(6Tセル)」が基本構造です。

CMOSインバーター1つあたり2つのMOSFETを使用するため、インバーター2つで4つ、アクセス用に2つ、合計6つのMOSFETで構成されます。

これら6つのMOSFETは、電源が供給されている間はデータを保持し続ける「フリップフロップ回路」を形成しており、DRAMのようなリフレッシュ動作は不要です。

SRAMのデータ保持状態

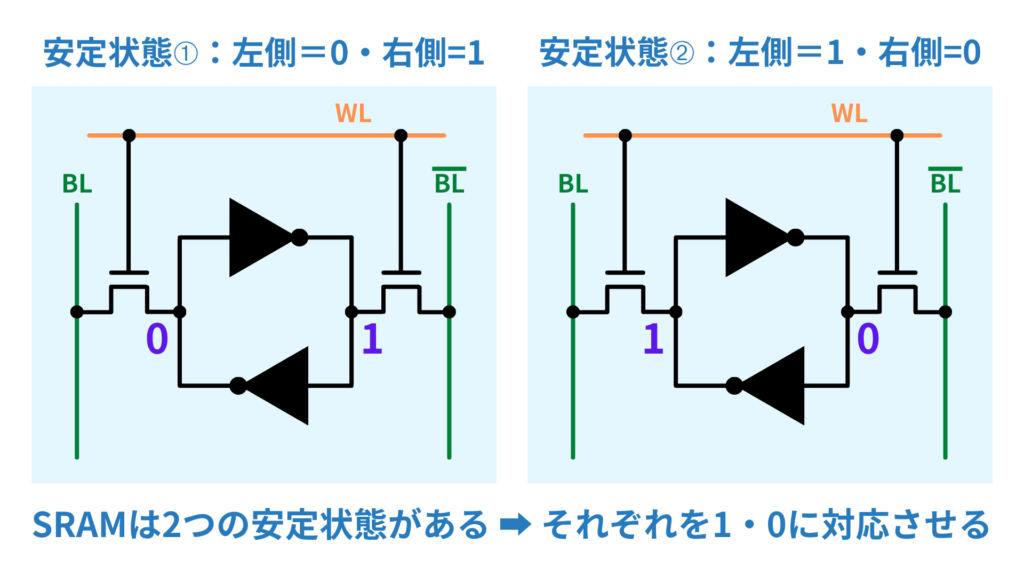

DRAMの場合、キャパシタに電荷が溜まった状態を1、電荷がない状態を0としてデータを記憶しています。では、SRAMはどうでしょうか。

SRAMは2つのインバーター回路が組み合わされているため、2つの安定状態があります。

- 安定状態➀:左側0・右側1

- 安定状態➁:左側1・右側0

左側の論理値が0、右側の論理値が1の安定状態。

安定状態➀の反対。左側が1、右側が0の安定状態。

SRAMでは2つの安定状態のうち、例えば安定状態➀を0、安定状態➁を1に対応させることでデータを記憶します。

SRAMの動作原理

SRAMには3つの動作があります。

- スタンバイ:回路が何もしていない状態

- 読み取り:データを読み取る

- 書き込み:データを書き込む

それぞれの動作原理を解説していきます。

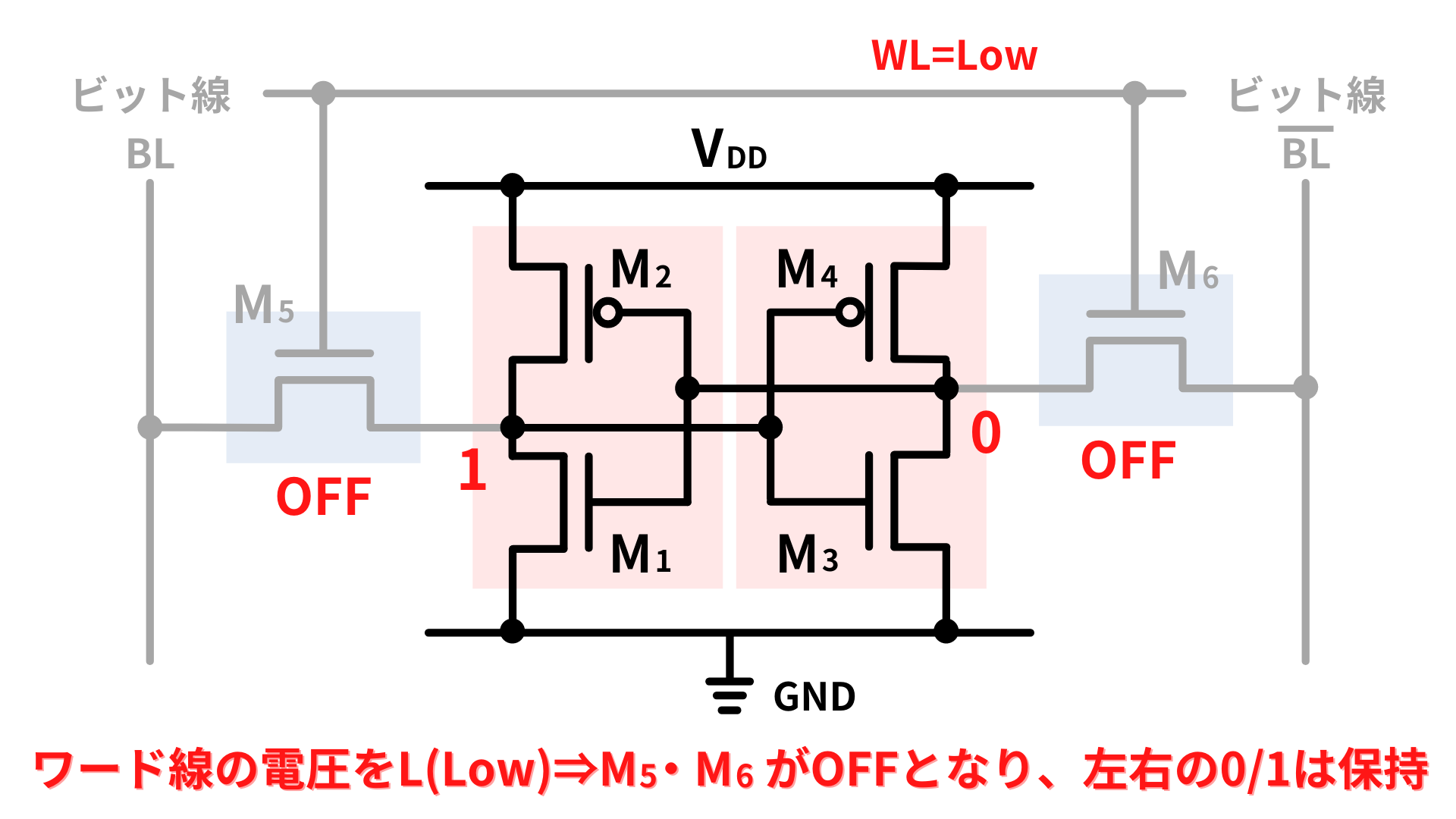

スタンバイ

説明のためにそれぞれのMOSFETをM1~M6と呼びます。

スタンバイは「左・右の論理値(1・0)を保持している状態」です。

スタンバイの動作原理は以下の通りです。

- ワード線の電圧をLow(L)にする

- M5・M6のMOSFETがOFFとなり、ビット線から切り離される

- 2つの交差したCMOSインバーターが1・0を保持し続ける

ビット線からCMOSインバーターが切り離されると1・0が保持される理由をもう少し詳しく見てみましょう。

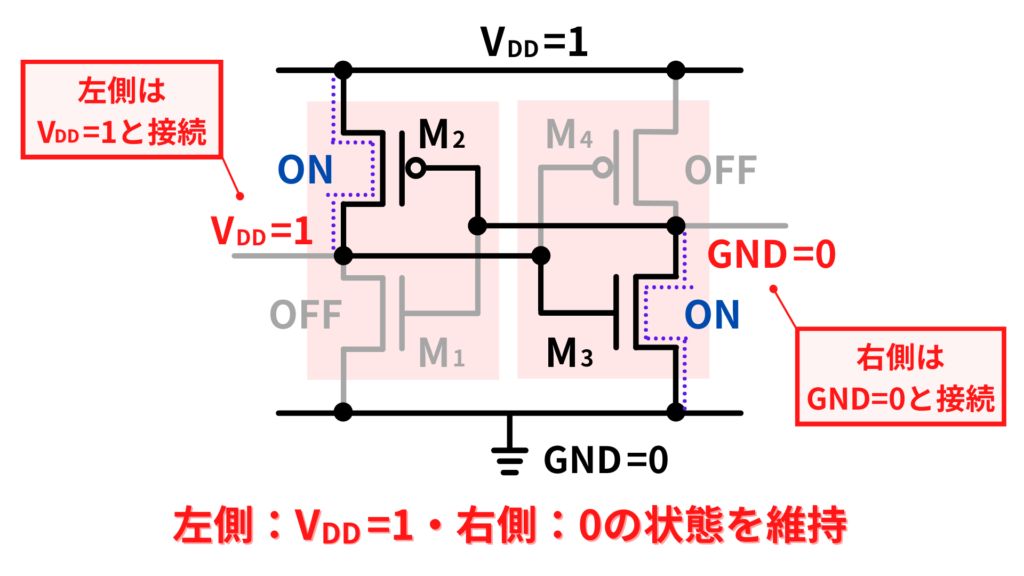

- 左側のCMOS

- 右側のCMOS

PMOSのゲートはGND=0に接続され、MOSFETがONとなる。VDDと接続され、VDD=1が保持される。

NMOSのゲートはVDD=1に接続され、MOSFETがONとなる。GNDと接続され、GND=0が保持される。

VDDの電源が入っている状態であれば、SRAMが左右の0・1は保持することが理解できたと思います。

読み取り

読み取りは「SRAMに記憶されている論理値(0・1)を読み取る動作」です。

読み取りでは、ワード線の電位をHighとしてMOSFETをONにした後、ビット線電位の上下で左右の1・0を読み取ります。

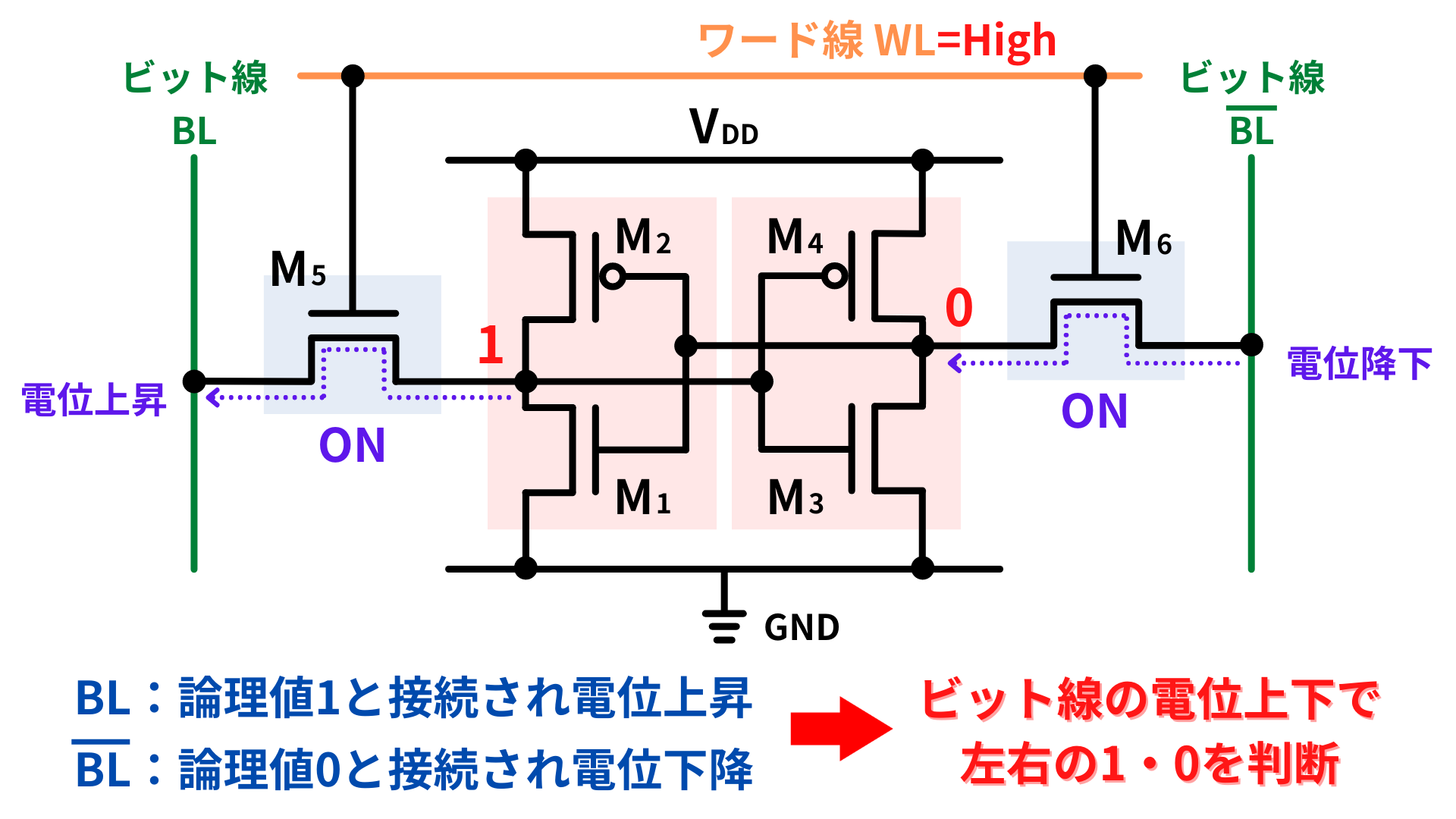

図の通り左側に1・右側に0を保持している状態を仮定します。読み取りの原理は以下の通りです。

- ワード線の電位をHighにする

- BL・BLの電位が変化

- BL・BLの電位変化を読み取る

CMOSインバーターと接続されたM5・M6のMOSFETがON状態となる。ワード線BL・BLとCMOSインバーターが接続される。

左側のBLは論理値1と接続され電位上昇する。右側のBLは論理値0と接続され電位降下する。

センスアンプによりビット線の電位(電圧)変化を読み取り1・0を判断する

SRAMは論理値1・0に応じたビットラインの電位変化を読み取ることで状態を判断しています。

書き込み

書き込みは「SRAMに論理値(0・1)を書き込む動作」です。

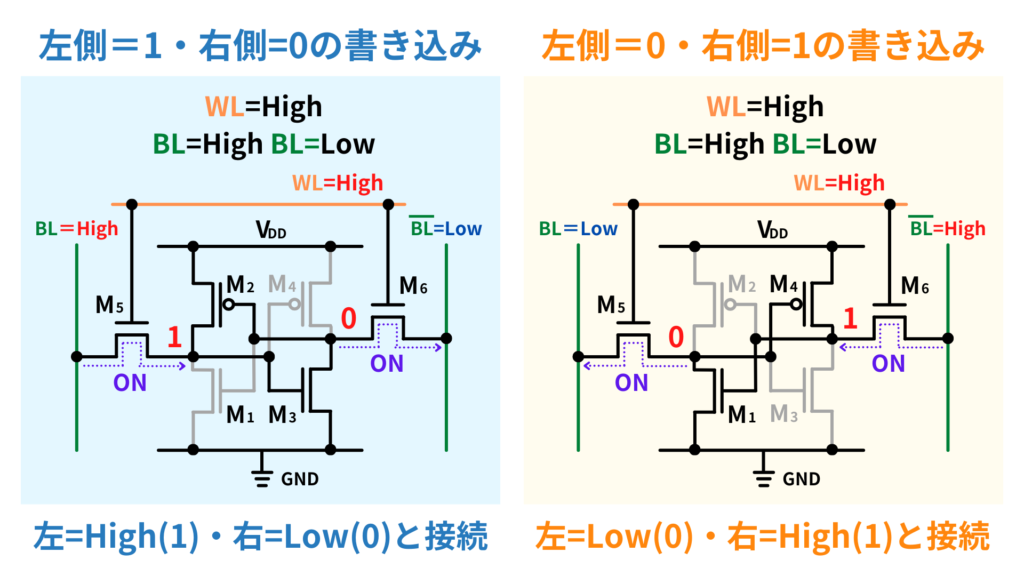

左側に1・右側に0を書き込む場合を例に、書き込み原理を解説します。

- ワード線WLをHighとする。

- BL=High・BL=Lowとする

M5・M6のMOSFETがONとなり、左右のCMOSがBL・BLと接続

左のCMOSは電位がHighのBLと接続され「1」を記録、右側は電位がLowのBLと接続され「0」を記録

この例とは逆に、左側に1、右側に0を書き込む場合はBL=Low・BL=HighとすればOKです。

前の講座

次の講座