デバイス1(コラボ図)

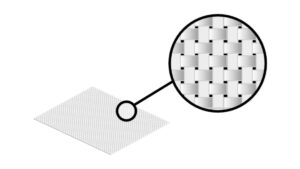

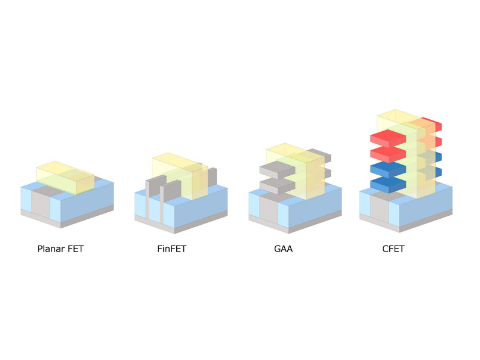

トランジスタ1:プレーナー・FinFET・GAA

半導体工場1

半導体工場2

半導体工場3

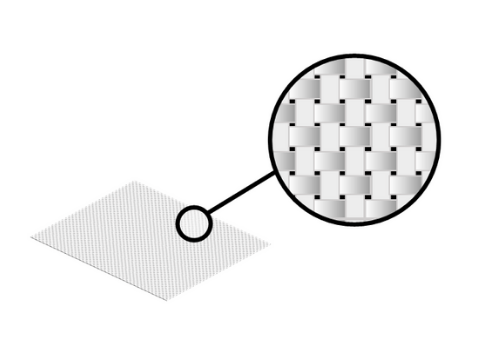

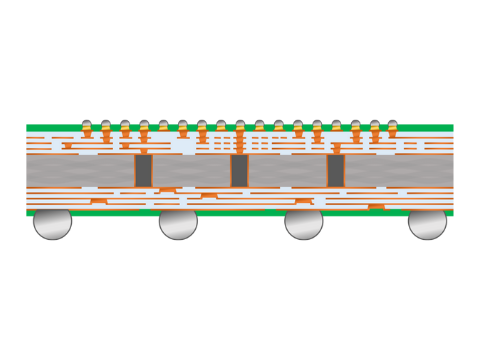

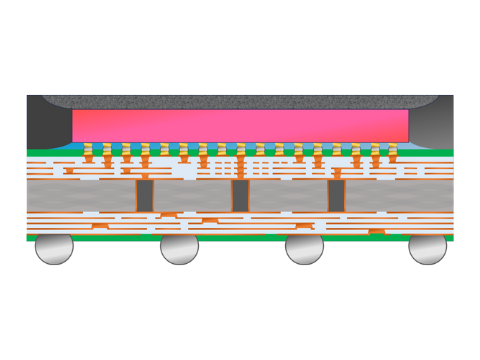

半導体パッケージ基板1

半導体パッケージ基板2

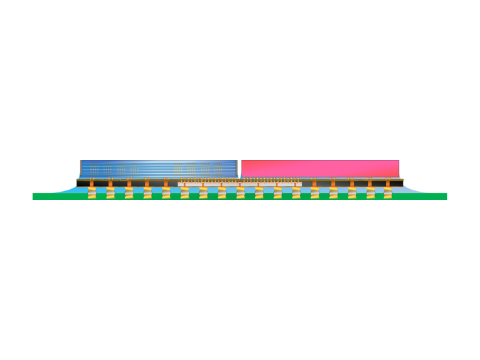

CoWoS-S

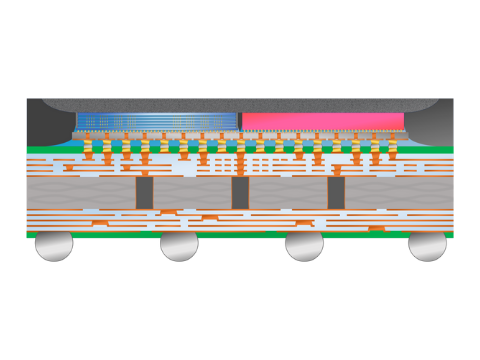

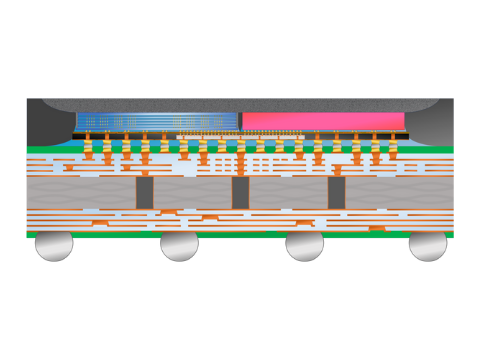

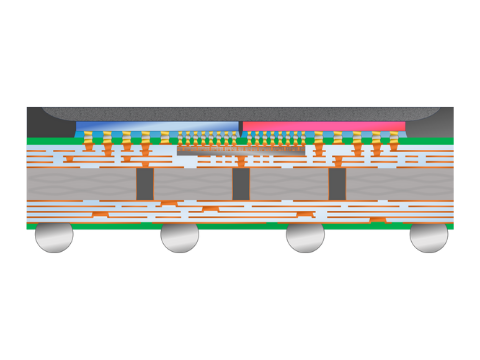

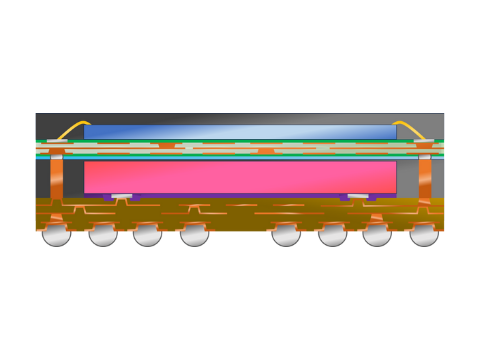

CoWoS-S(断面図)

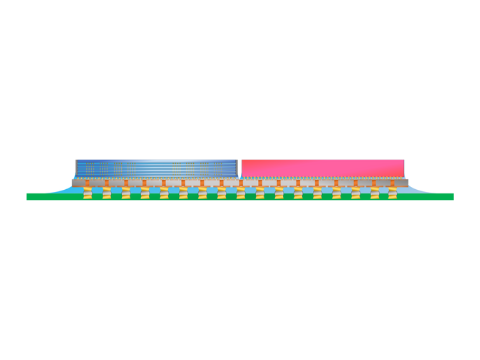

CoWoS-R

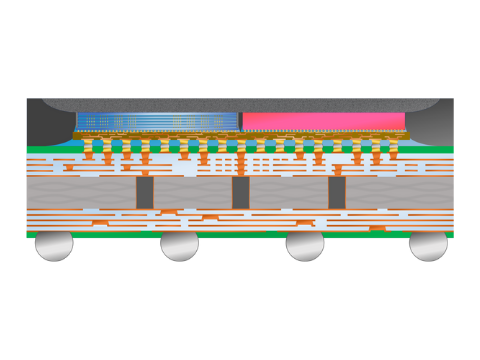

CoWoS-R(断面図)

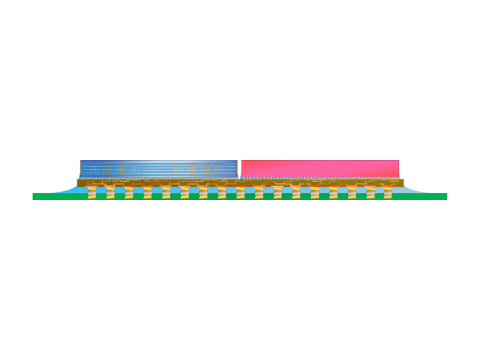

CoWoS-L

CoWoS-L(断面図)

EMIB

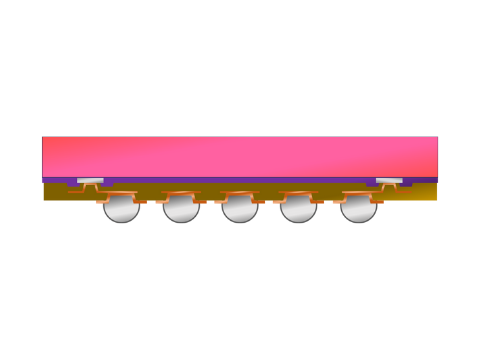

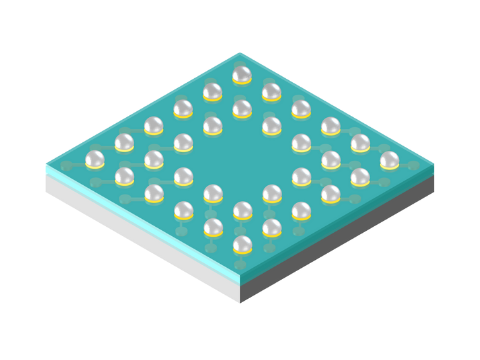

WL-CSP(Wafer Level Chip Size Package)

FO-WLP(Fan-Out Wafer Level Package)

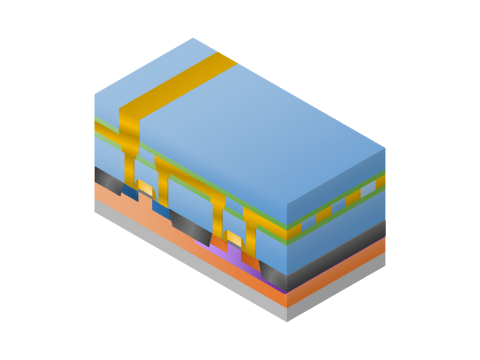

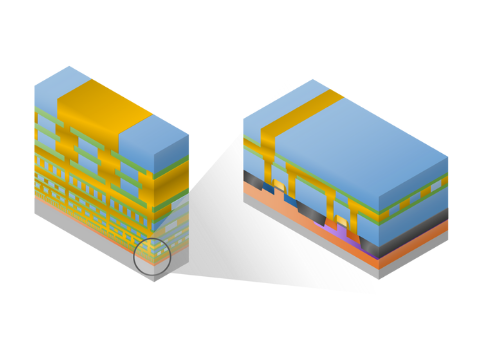

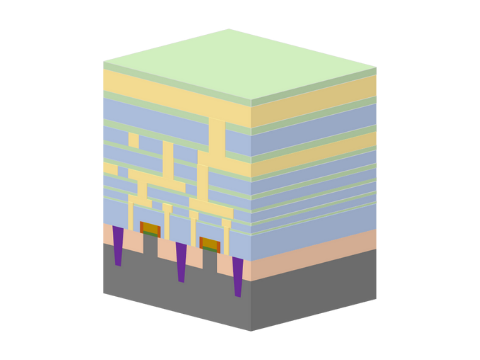

半導体配線構造1

半導体配線構造2

半導体配線構造3

InFO-PoP(Package on Package)

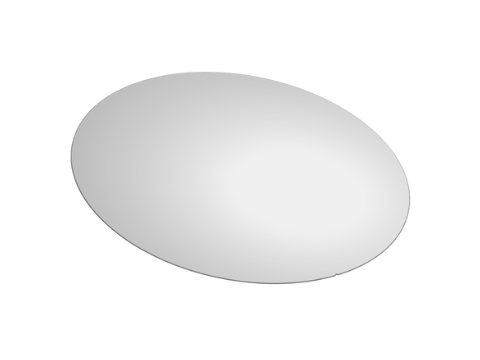

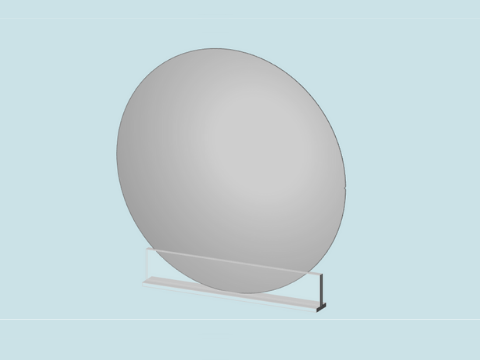

シリコンウェーハ(ノッチ)

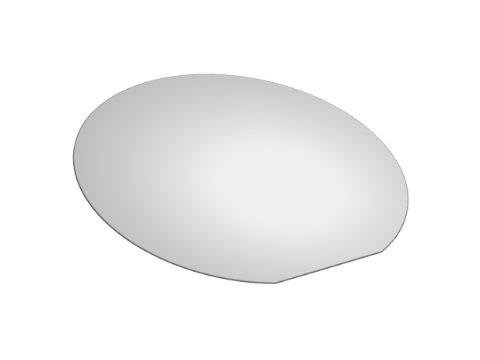

シリコンウェーハ(オリフラ)

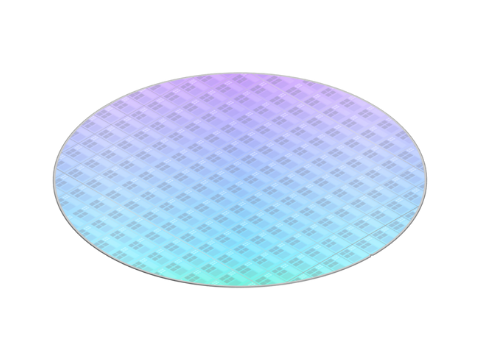

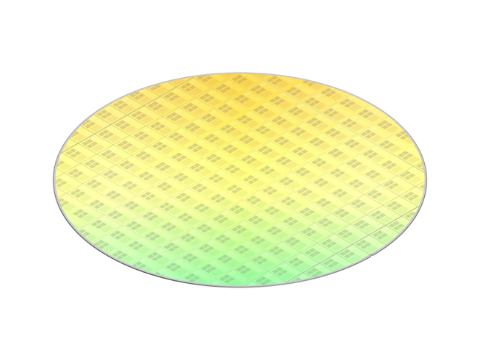

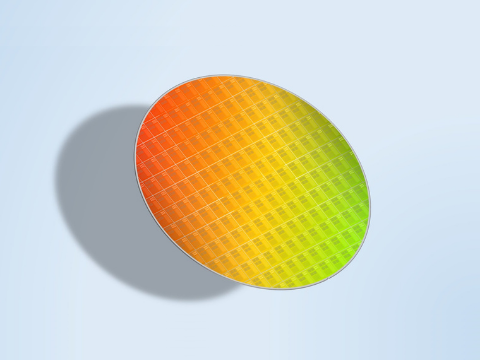

シリコンウェーハ(パターン付き)-1

シリコンウェーハ(パターン付き)-2

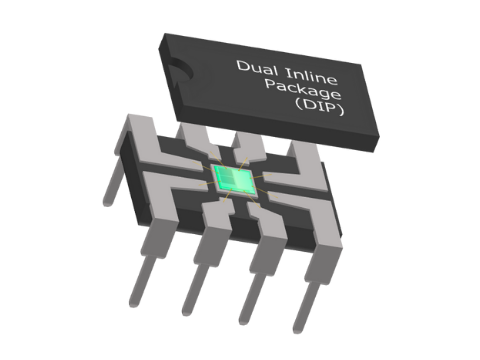

Dual inline Package(DIP)-1

Dual inline Package(DIP)-2

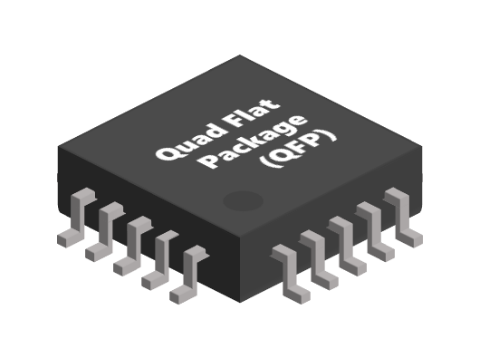

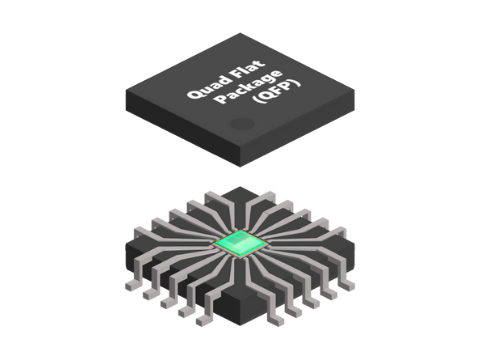

Quad Flat Package-1

Quad Flat Package-2

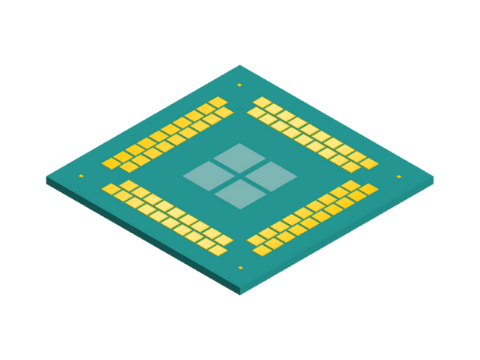

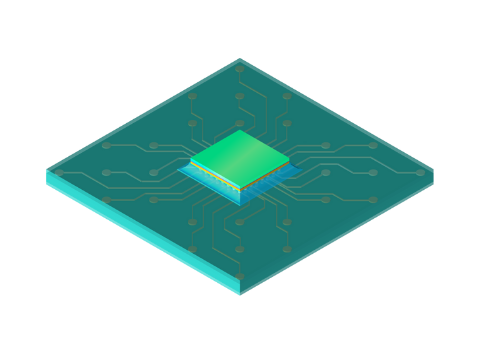

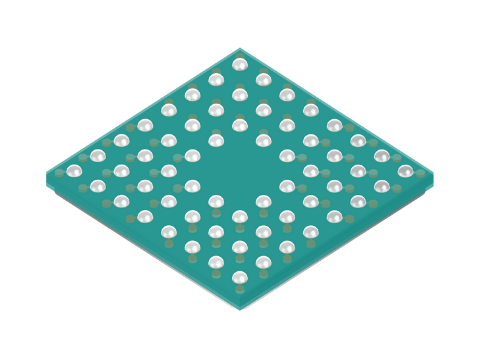

FC-BGA基板-1

FC-BGA基板-2

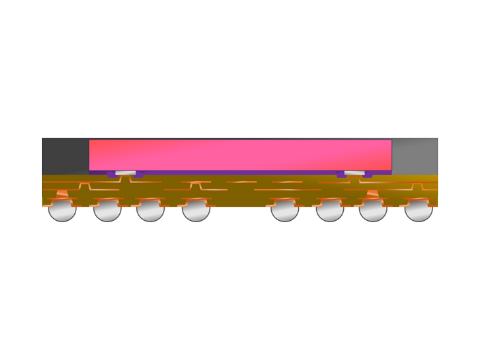

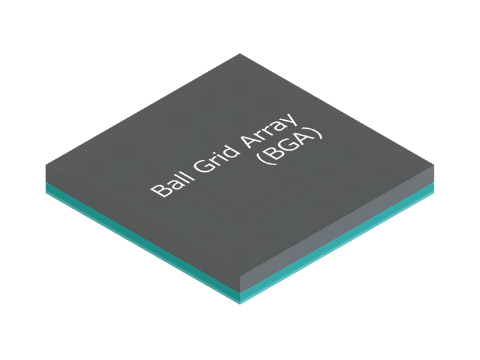

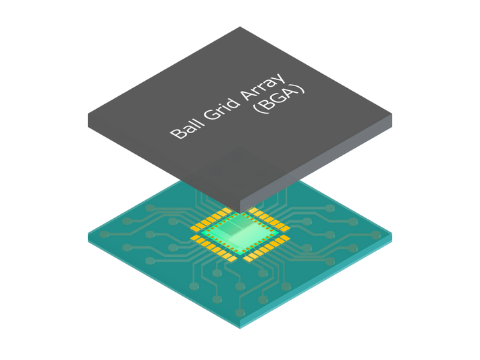

Ball Grid Array(BGA)-1

Ball Grid Array(BGA)-2

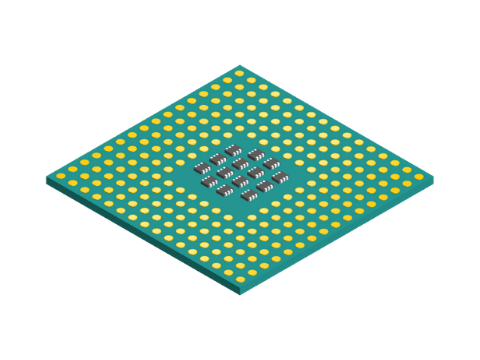

Ball Grid Array(BGA)-3

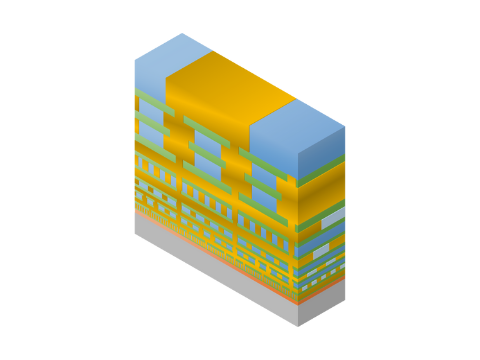

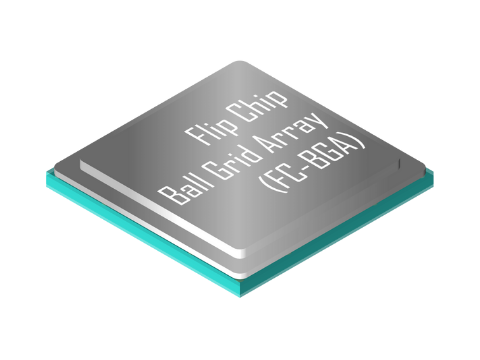

Flip-Chip Ball Grid Array(FC-BGA)-1

Flip-Chip Ball Grid Array(FC-BGA)-2

Flip-Chip Ball Grid Array(FC-BGA)-3

トランジスタ2:プレーナー・FinFET・GAA

半導体配線構造4

シリコンウェーハ(スタンド付き)

ガラスウェーハ・銅(Cu)メッキウェーハ

ガラスウェーハ・炭化ケイ素(SiC)ウェーハ

シリコンウェーハ(パターン付き)-3

SiCウェーハ