全イラスト・素材一覧(All)

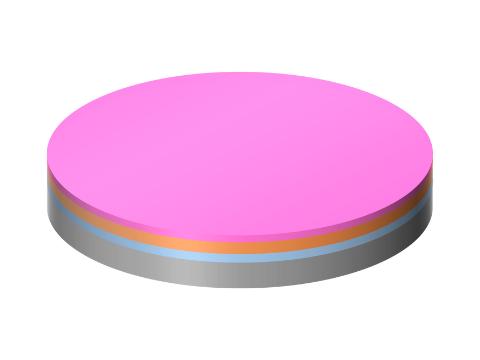

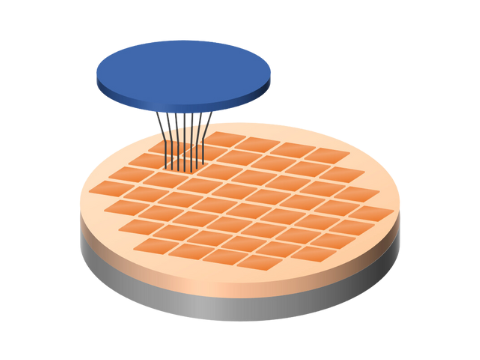

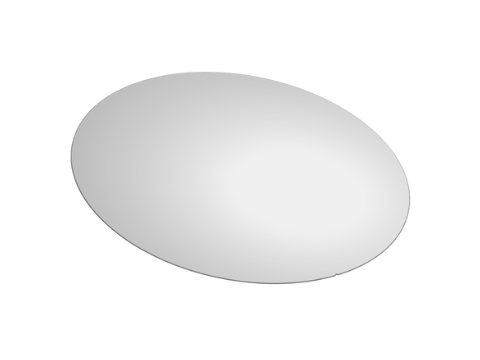

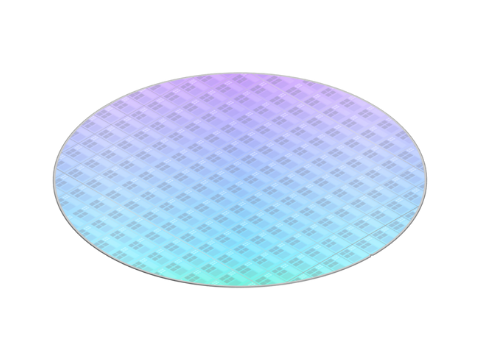

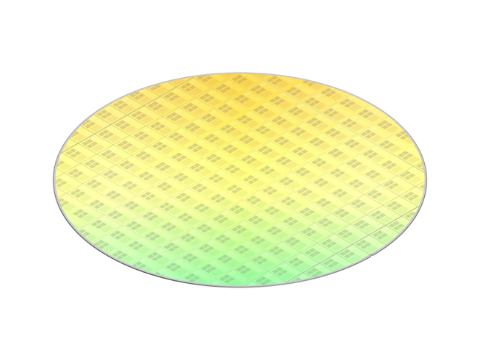

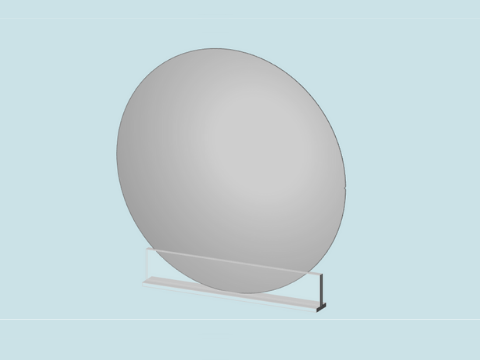

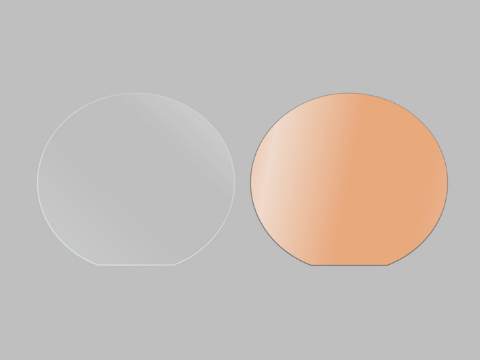

シリコンウェーハ

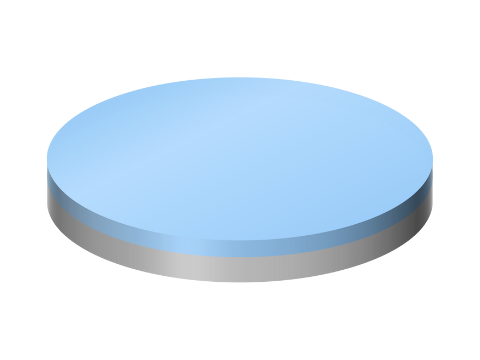

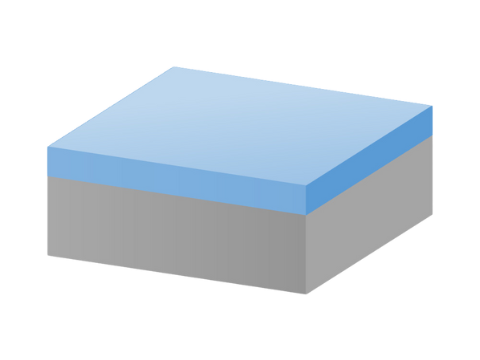

シリコンウェーハ(酸化膜付き)

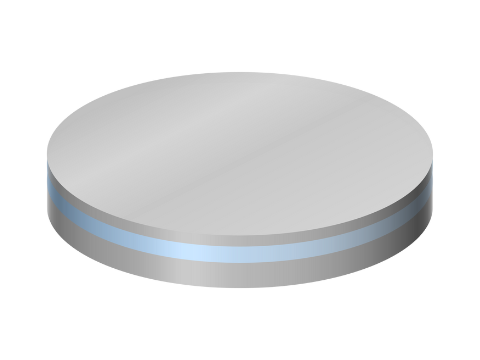

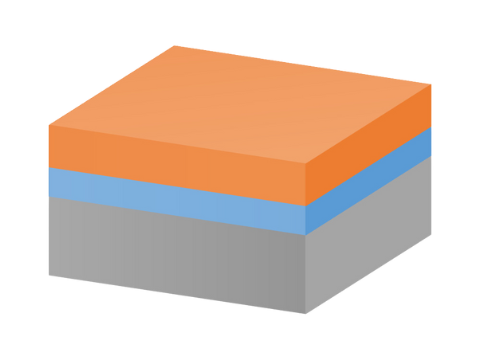

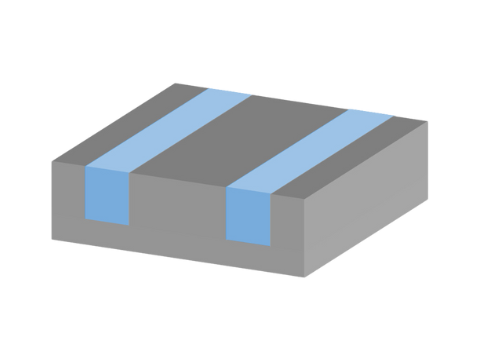

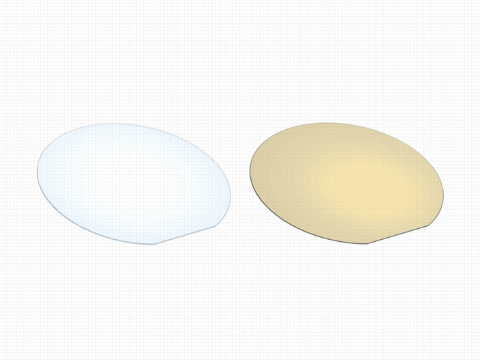

SOIウェーハ

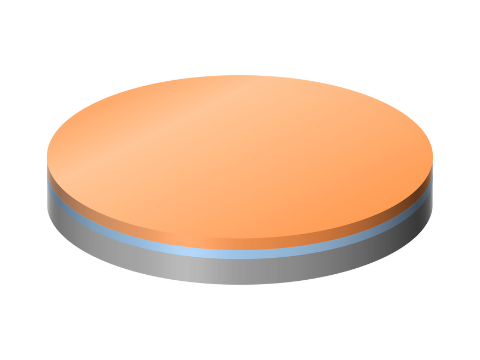

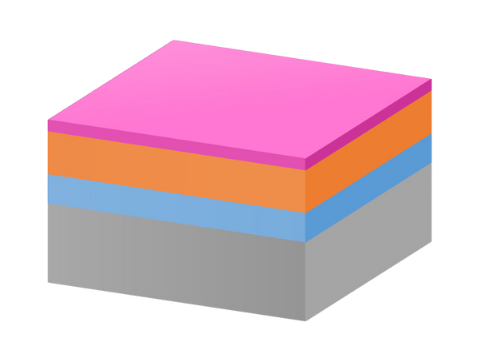

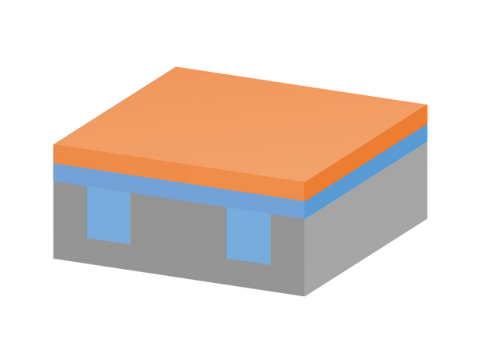

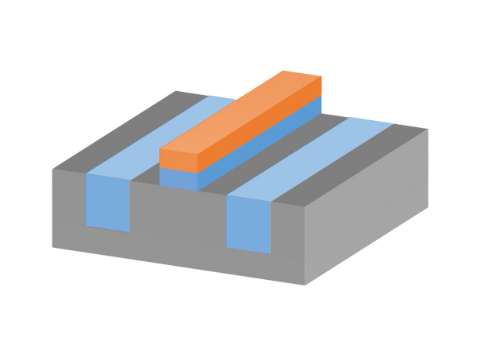

膜付きシリコンウェーハ(3層)

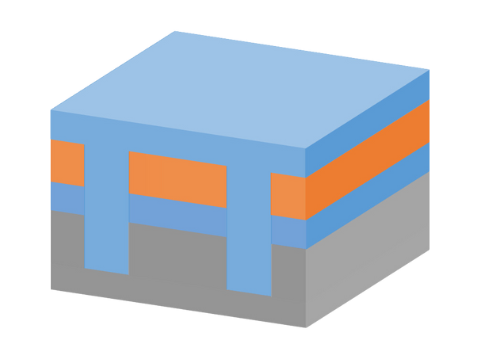

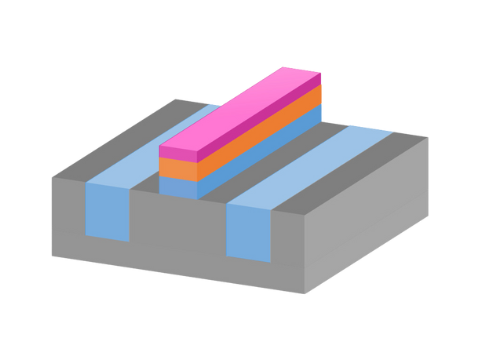

膜付きシリコンウェーハ(4層)

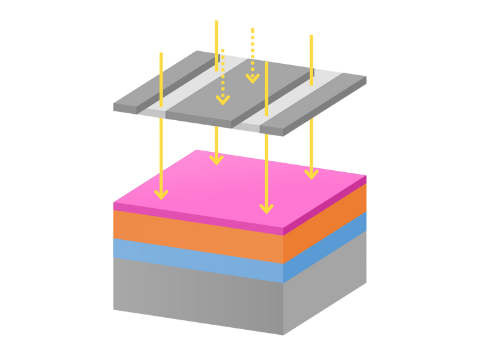

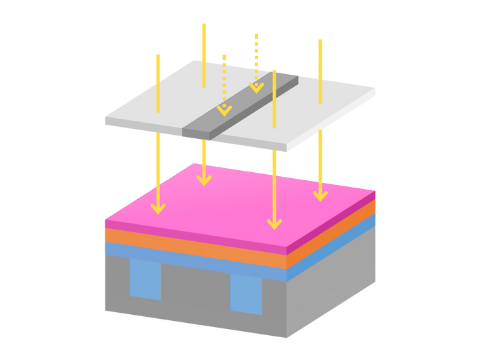

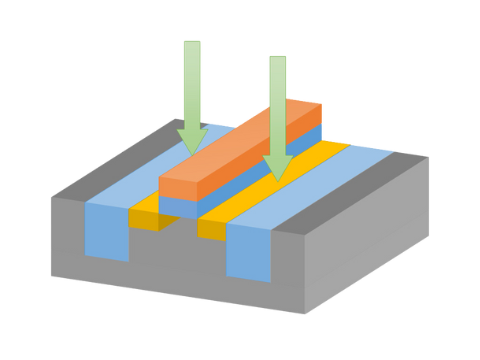

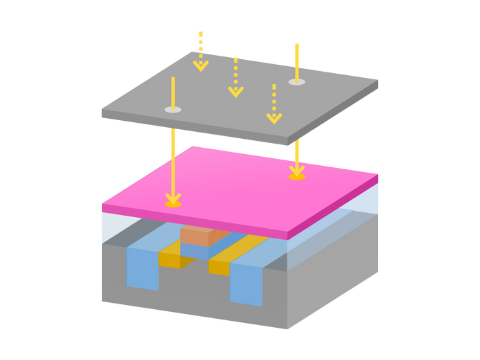

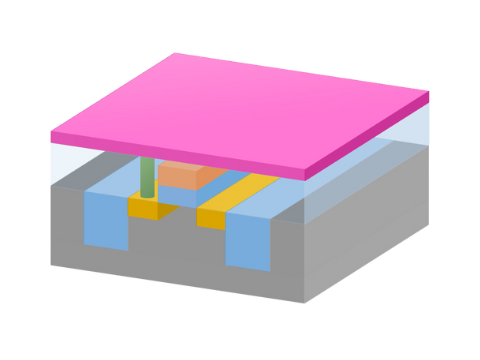

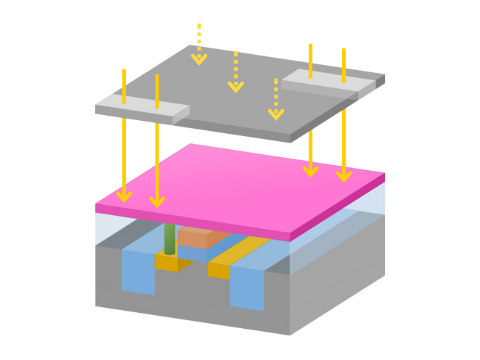

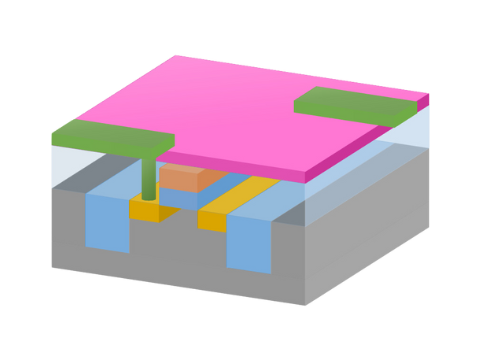

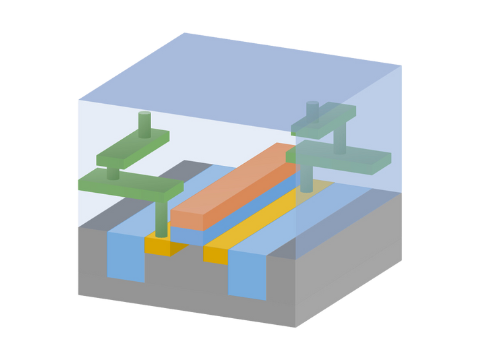

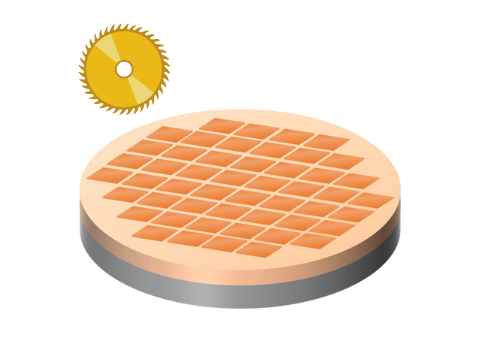

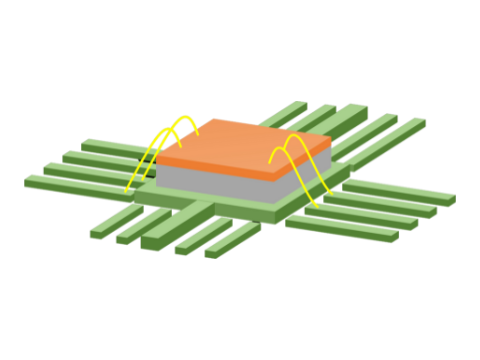

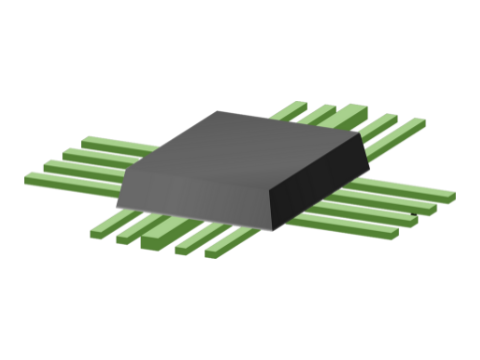

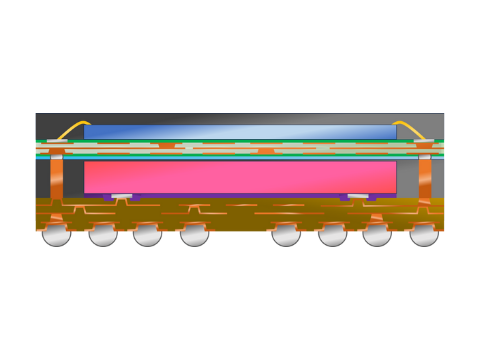

半導体製造の流れ1

半導体製造の流れ2

半導体製造の流れ3

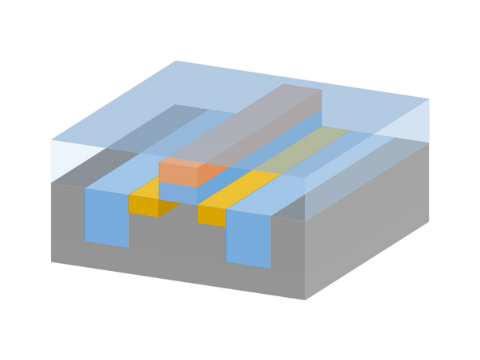

半導体製造の流れ4

半導体製造の流れ5

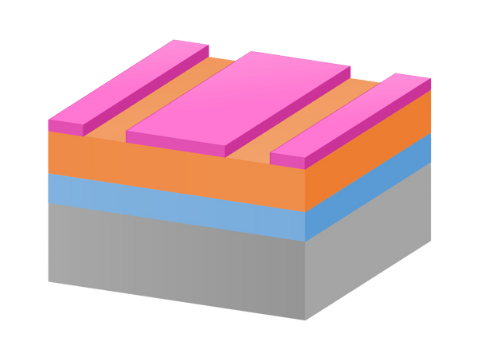

半導体製造の流れ6

半導体製造の流れ7

半導体製造の流れ8

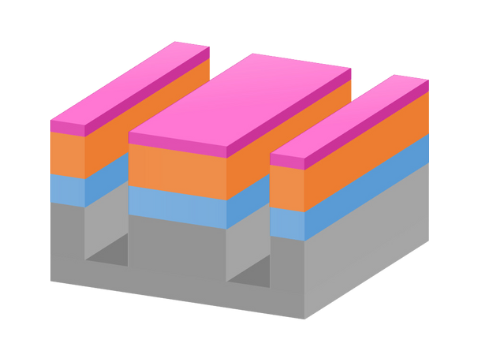

半導体製造の流れ9

半導体製造の流れ10

半導体製造の流れ11

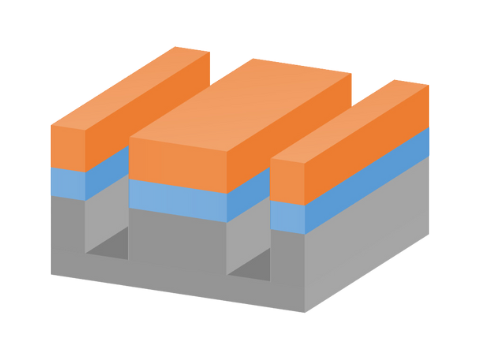

半導体製造の流れ12

半導体製造の流れ13

半導体製造の流れ14

半導体製造の流れ15

半導体製造の流れ16

半導体製造の流れ17

半導体製造の流れ18

半導体製造の流れ19

半導体製造の流れ20

半導体製造の流れ21

半導体製造の流れ22

半導体製造の流れ23

半導体製造の流れ24

半導体製造の流れ25

半導体製造の流れ26

半導体製造の流れ27

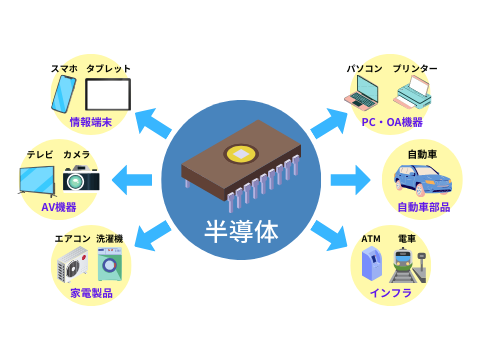

半導体の用途

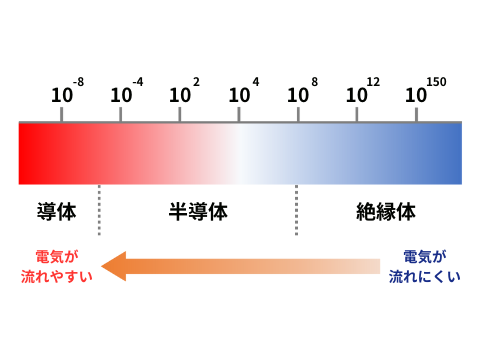

半導体の電気抵抗率

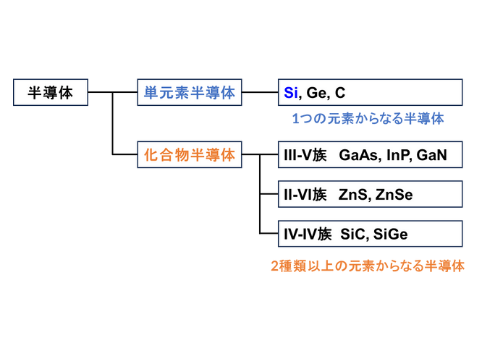

半導体の材料

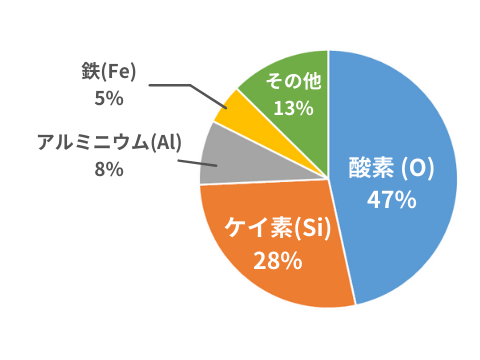

地殻中の元素存在比

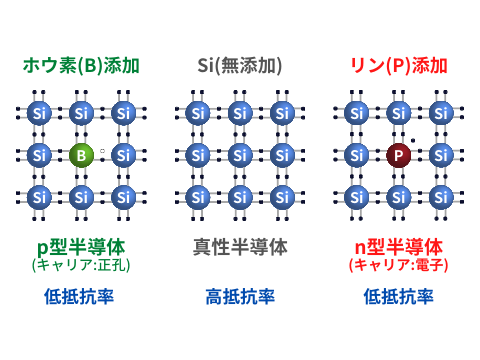

シリコンの抵抗率制御

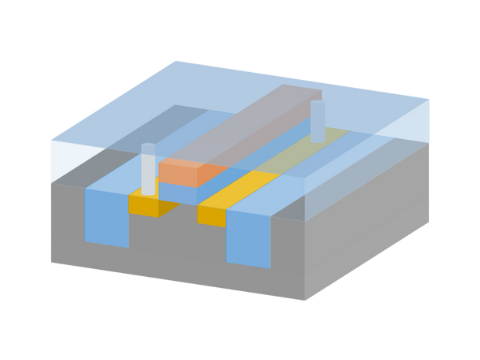

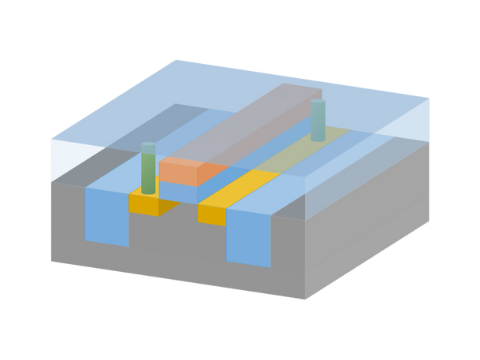

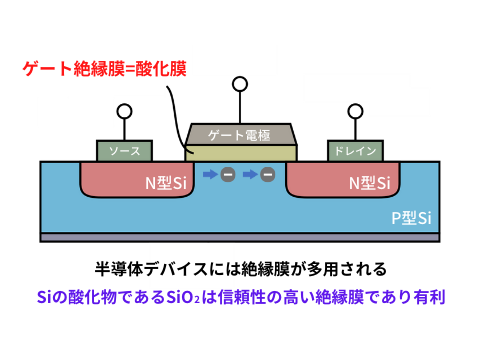

MOSFETの構造と酸化膜

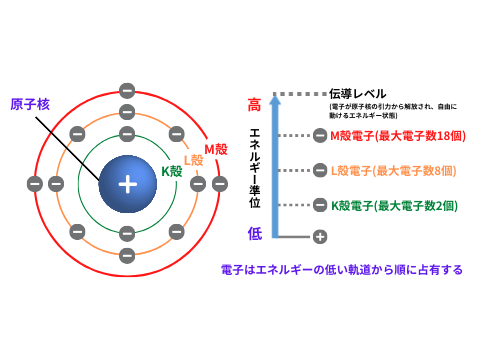

原子の基本構造

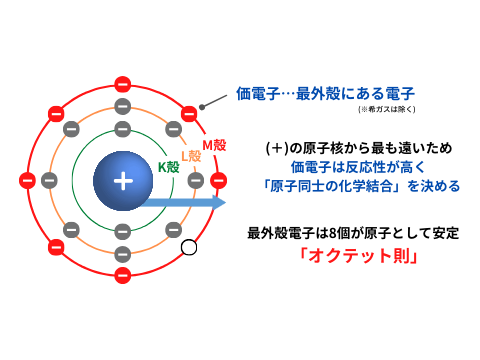

価電子とオクテット則

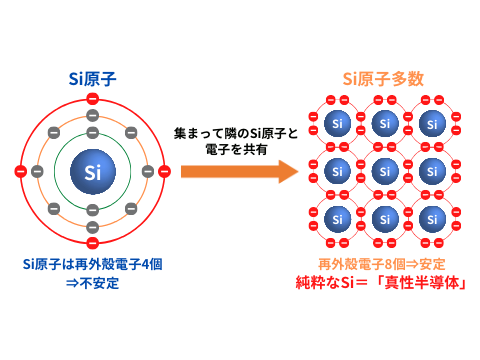

シリコンの構造:共有結合

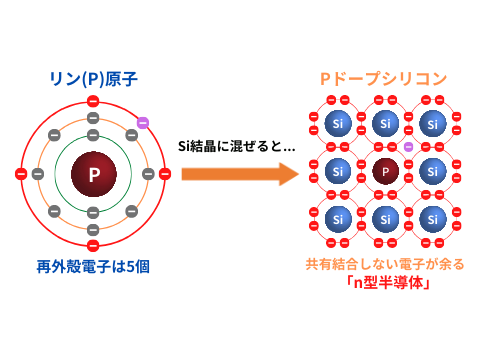

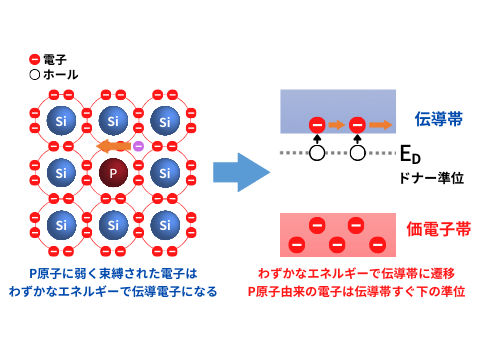

n型半導体の電子配置

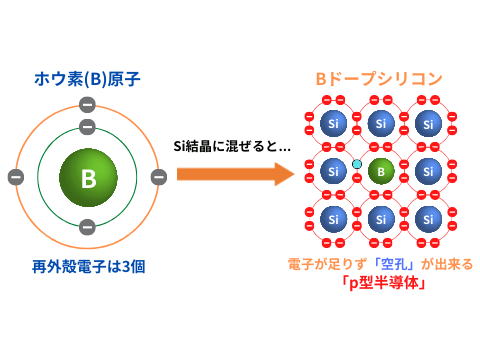

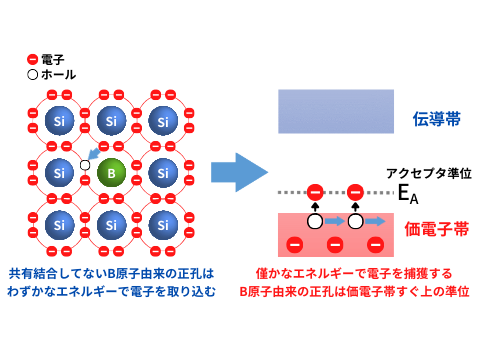

p型半導体の電子配置

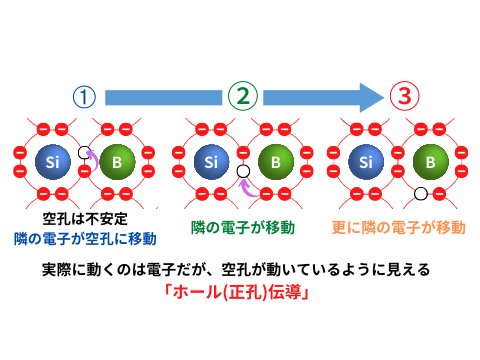

ホール(正孔)伝導の仕組み

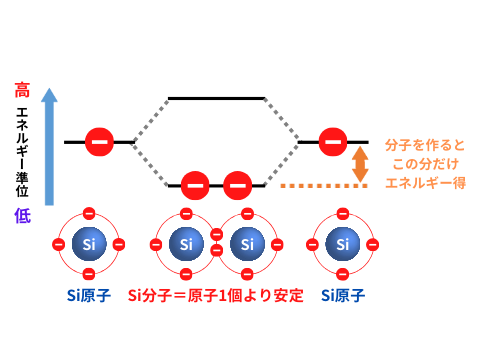

共有結合による原子の安定化

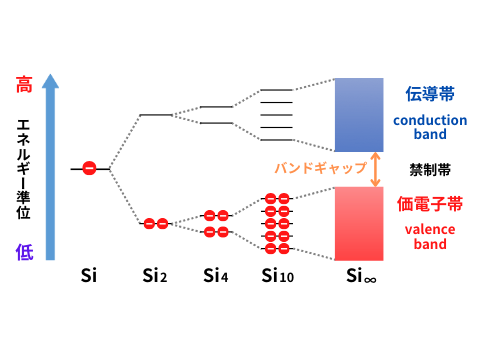

原子の結合によるエネルギーバンド形成

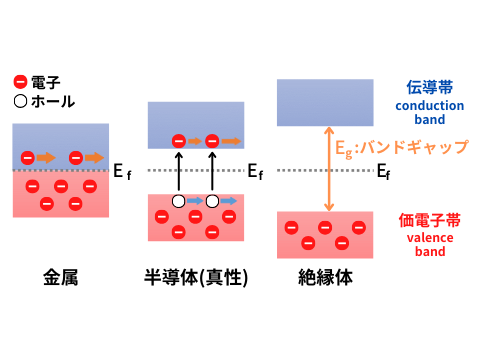

金属・半導体・絶縁体のバンド構造1

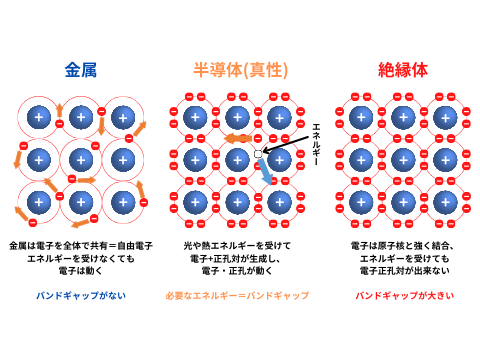

金属・半導体・絶縁体のバンド構造2

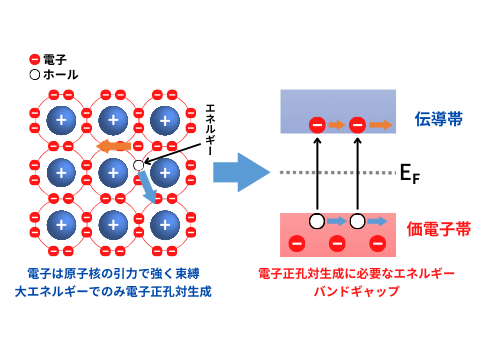

真性半導体のバンド構造

n型半導体のバンド構造

p型半導体のバンド構造

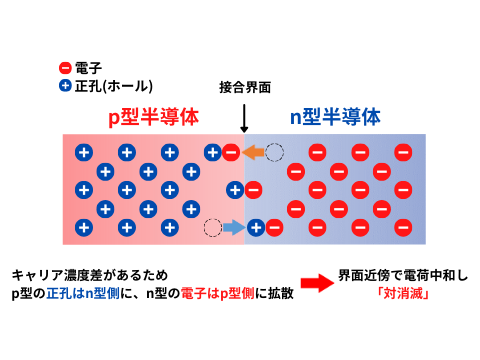

pn接合による多数キャリアの拡散

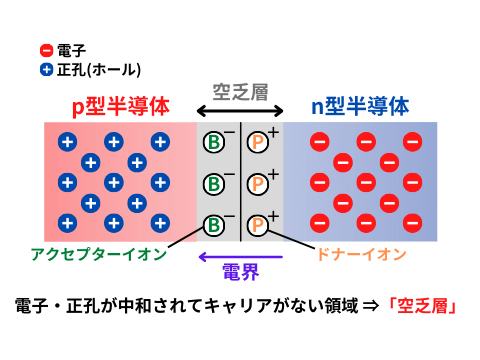

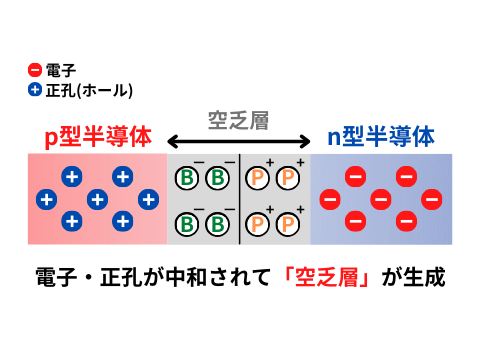

pn接合による空乏層の生成

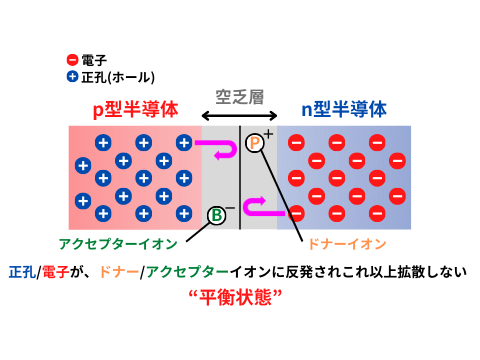

pn接合の平衡状態

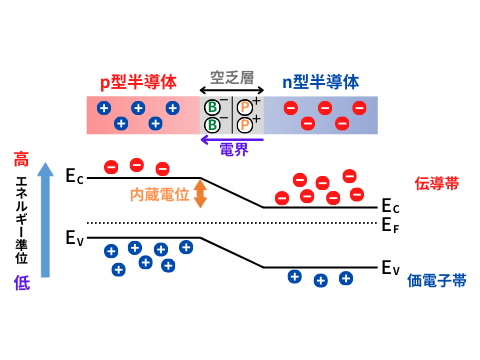

pn接合のバンド図

pn接合による空乏層の生成

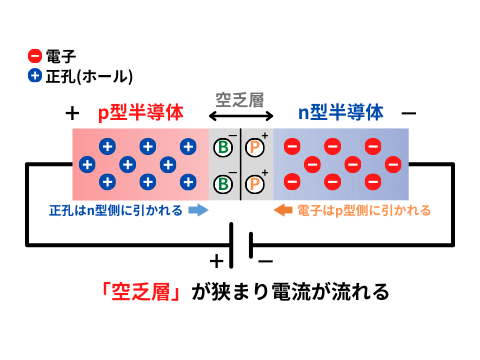

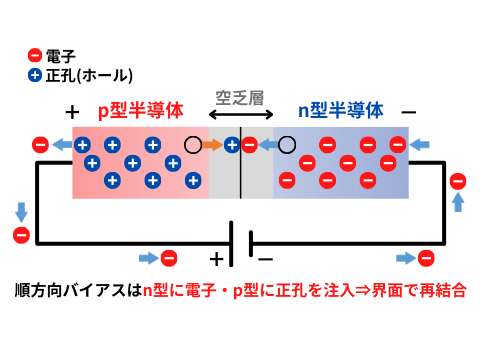

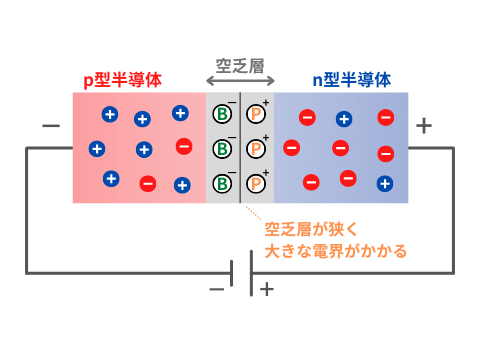

pn接合の順方向バイアス

順方向バイアスの電子の流れ

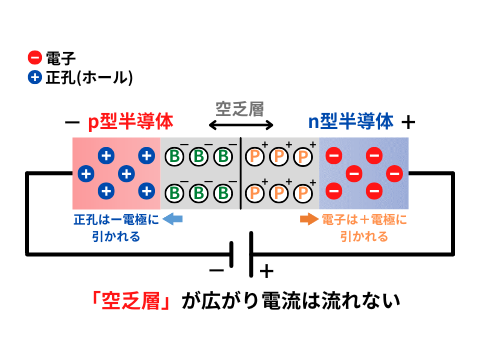

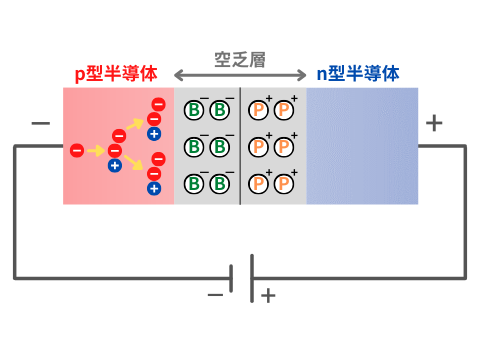

pn接合の逆方向バイアス

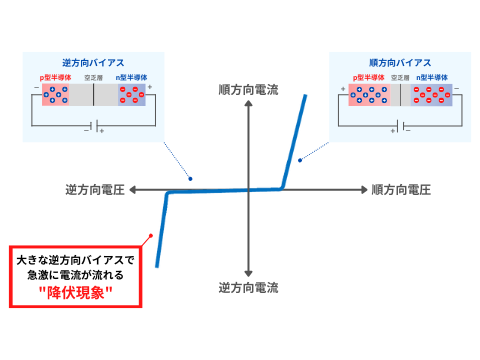

半導体の降伏現象

ツェナー降伏とアバランシェ降伏

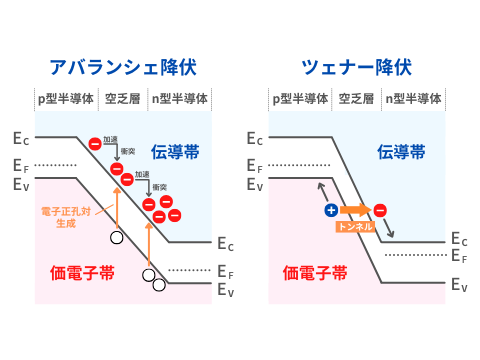

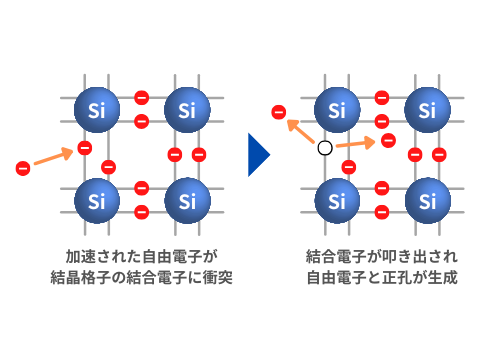

アバランシェ降伏の原理

電子雪崩の原理

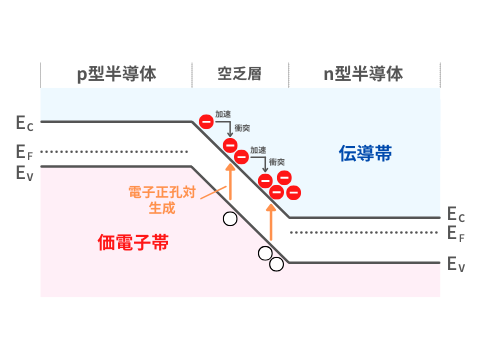

アバランシェ降伏のバンド図

ツェナー降伏の原理

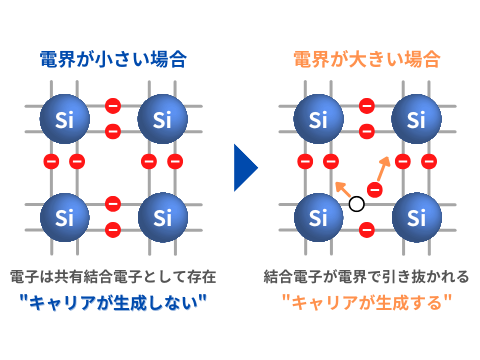

ツェナー降伏におけるキャリア発生の模式図

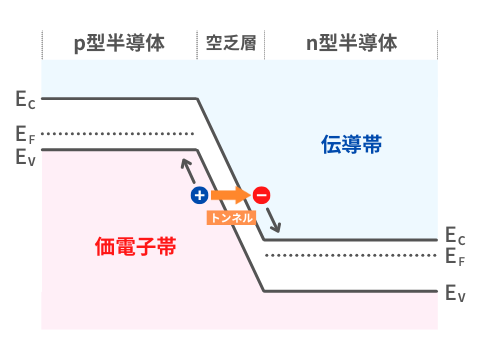

ツェナー降伏のバンド図

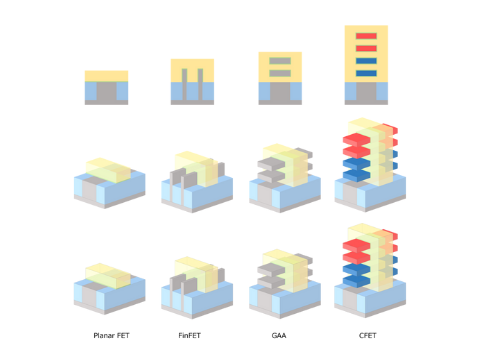

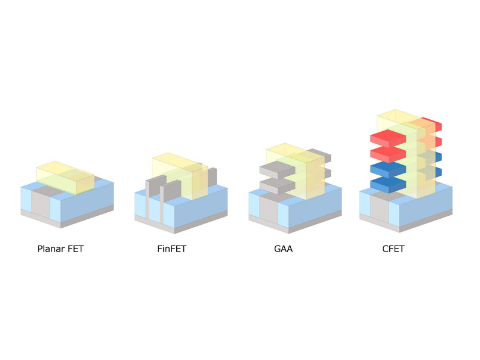

トランジスタ1:プレーナー・FinFET・GAA

半導体工場1

半導体工場2

半導体工場3

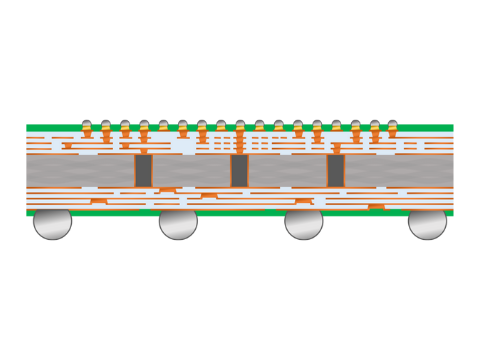

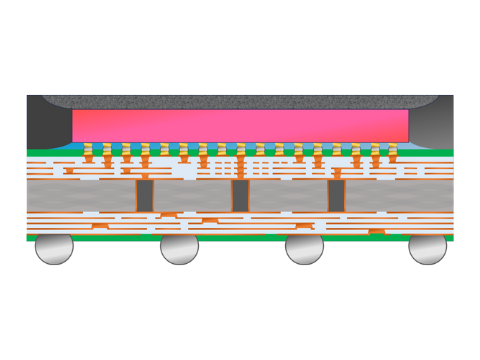

半導体パッケージ基板1

半導体パッケージ基板2

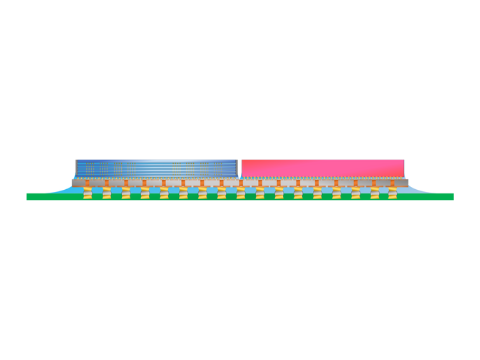

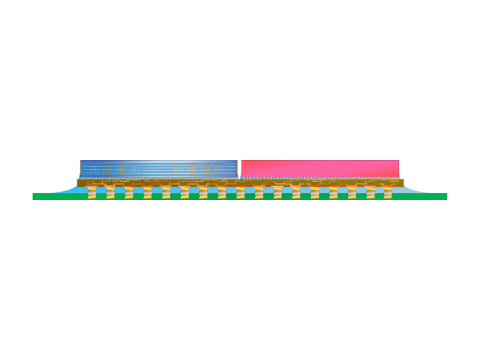

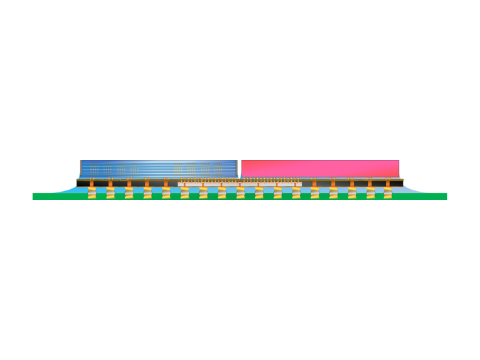

CoWoS-S

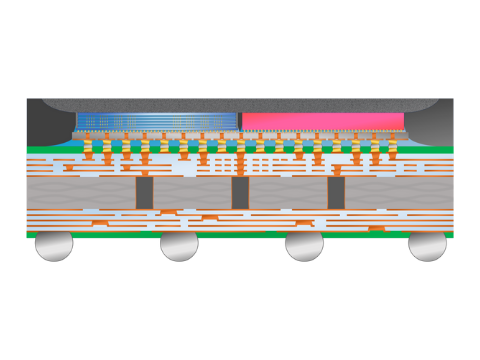

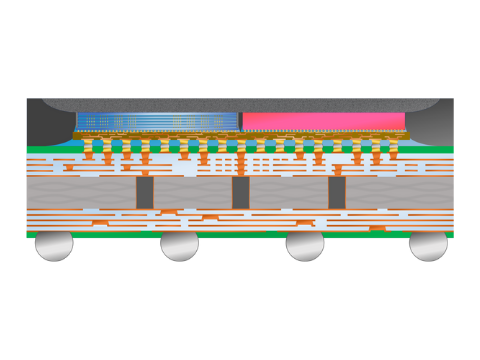

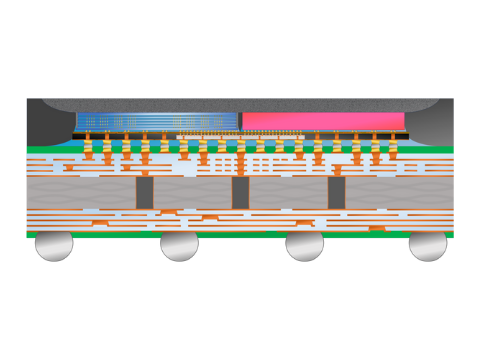

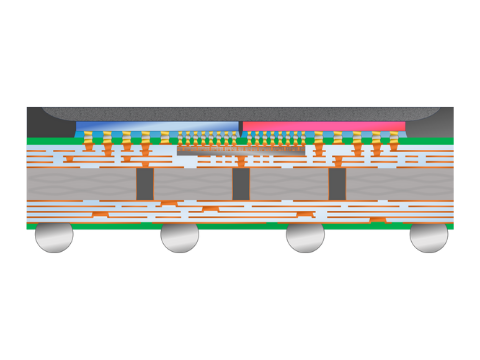

CoWoS-S(断面図)

CoWoS-R

CoWoS-R(断面図)

CoWoS-L

CoWoS-L(断面図)

EMIB

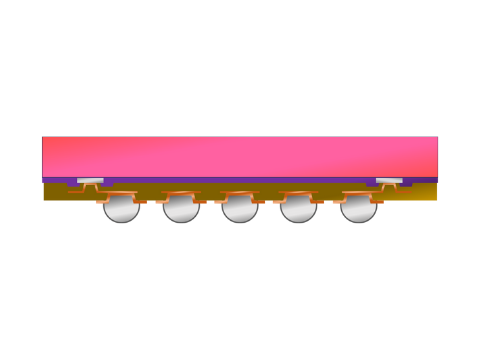

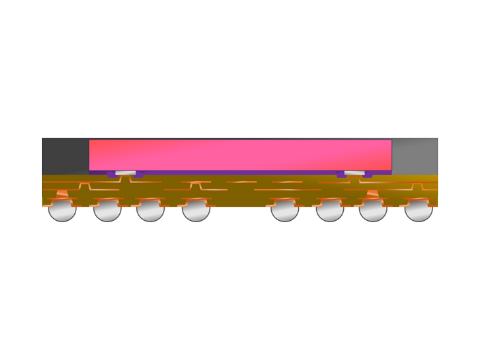

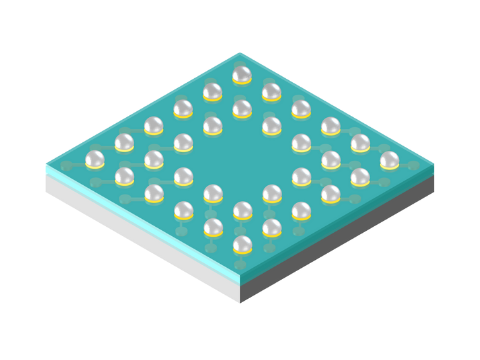

WL-CSP(Wafer Level Chip Size Package)

FO-WLP(Fan-Out Wafer Level Package)

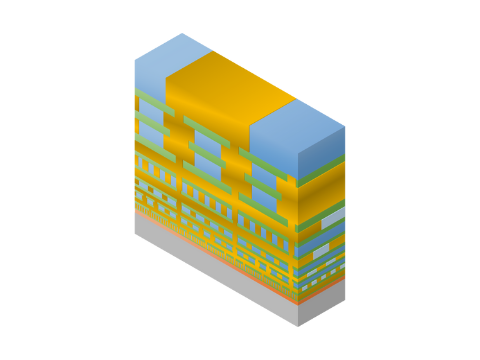

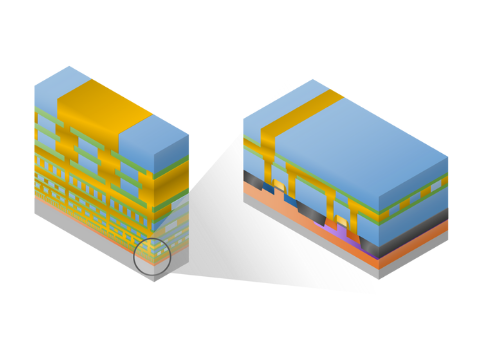

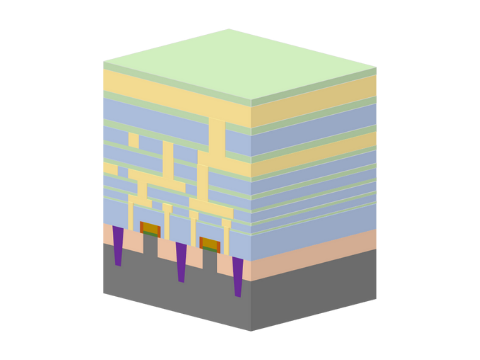

半導体配線構造1

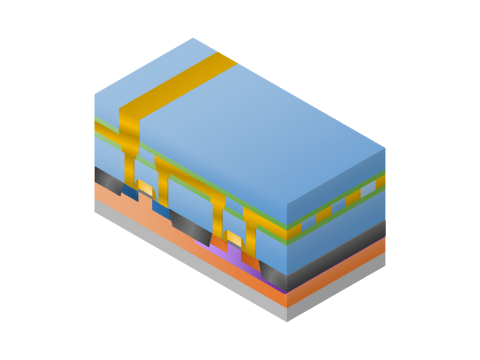

半導体配線構造2

半導体配線構造3

InFO-PoP(Package on Package)

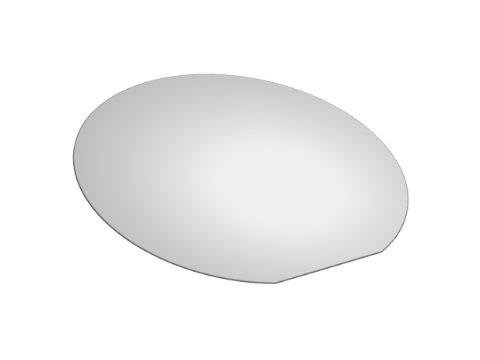

シリコンウェーハ(ノッチ)

シリコンウェーハ(オリフラ)

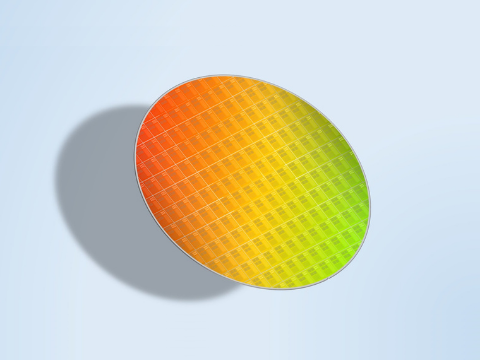

シリコンウェーハ(パターン付き)-1

シリコンウェーハ(パターン付き)-2

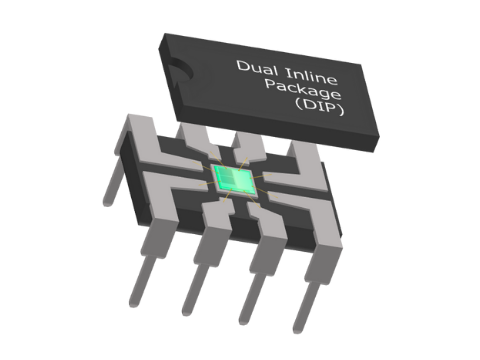

Dual inline Package(DIP)-1

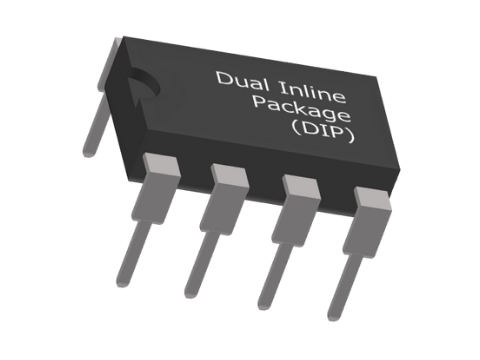

Dual inline Package(DIP)-2

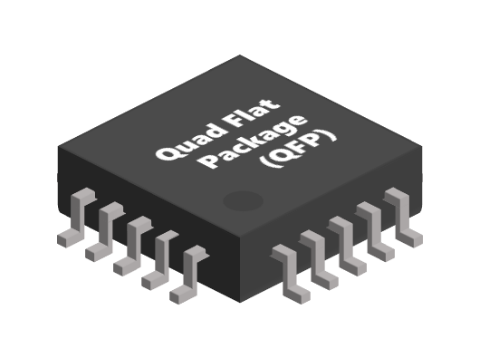

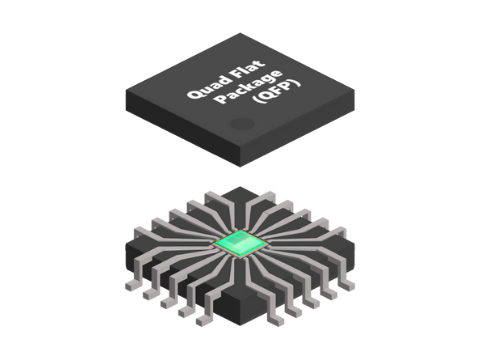

Quad Flat Package-1

Quad Flat Package-2

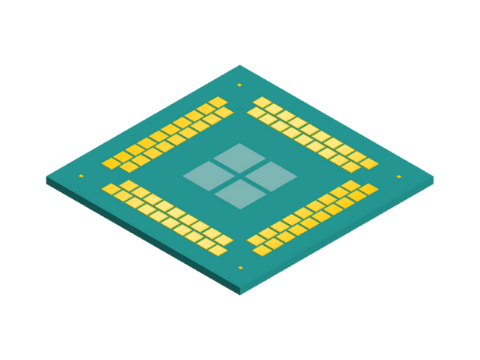

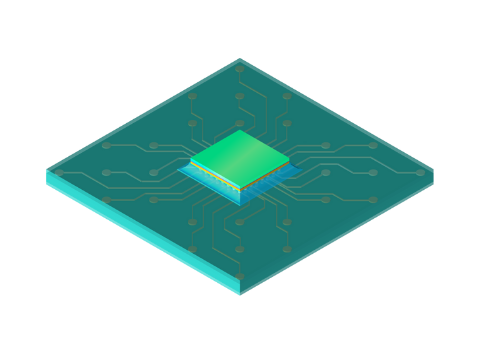

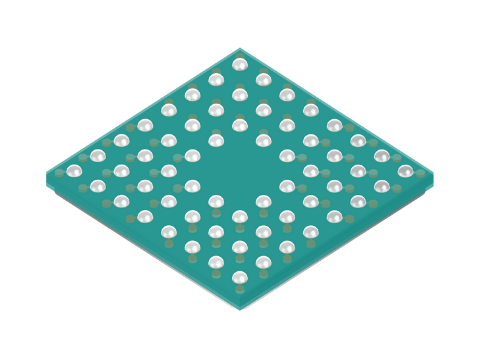

FC-BGA基板-1

FC-BGA基板-2

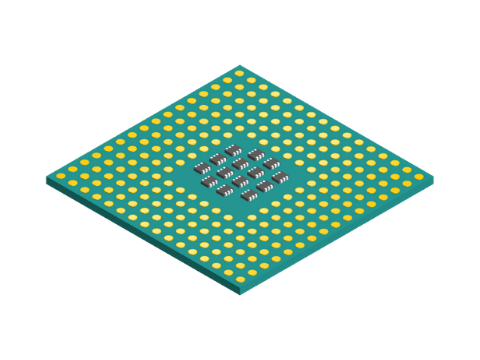

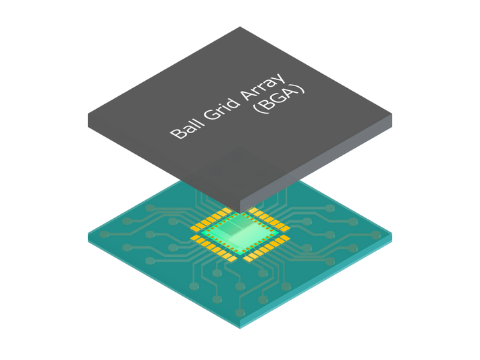

Ball Grid Array(BGA)-1

Ball Grid Array(BGA)-2

Ball Grid Array(BGA)-3

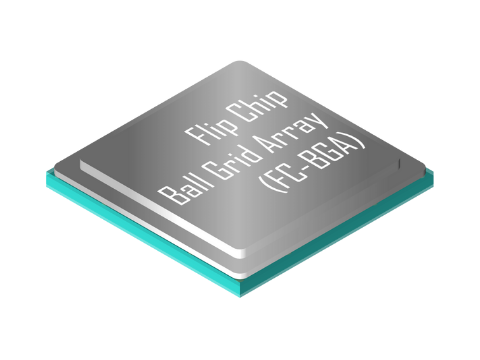

Flip-Chip Ball Grid Array(FC-BGA)-1

Flip-Chip Ball Grid Array(FC-BGA)-2

Flip-Chip Ball Grid Array(FC-BGA)-3

トランジスタ2:プレーナー・FinFET・GAA

半導体配線構造4

シリコンウェーハ(スタンド付き)

ガラスウェーハ・銅(Cu)メッキウェーハ

ガラスウェーハ・炭化ケイ素(SiC)ウェーハ

シリコンウェーハ(パターン付き)-3

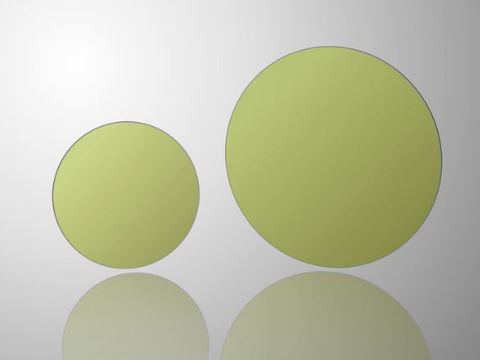

SiCウェーハ

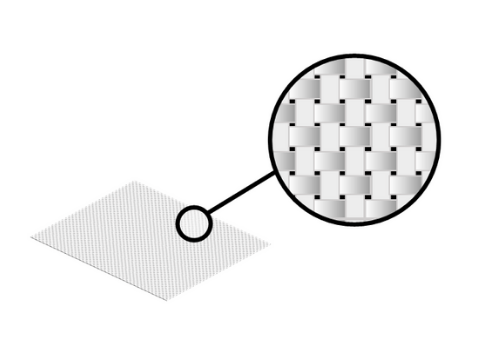

ガラスクロス

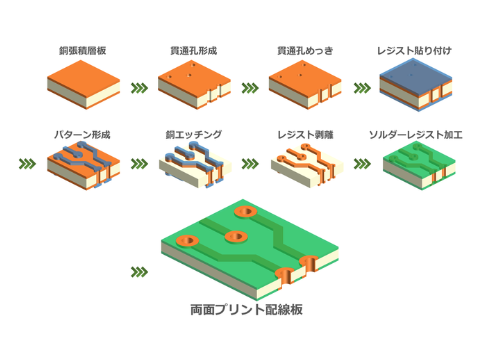

両面プリント配線板

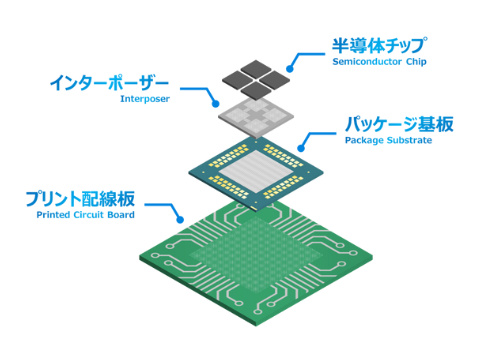

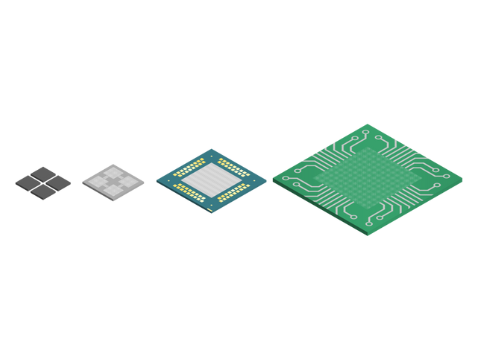

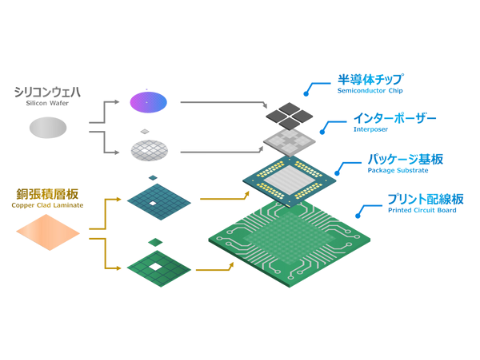

2.5D半導体パッケージ1

2.5D半導体パッケージ2

2.5D半導体パッケージ3

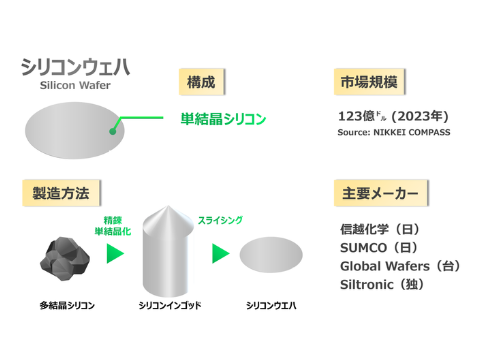

シリコンウェーハ

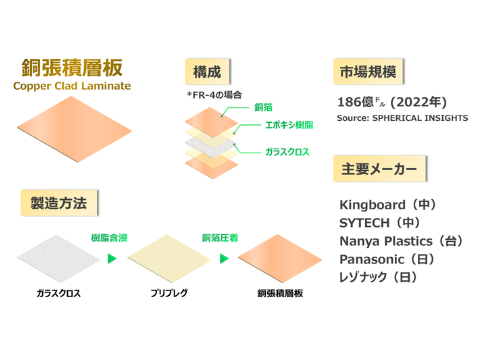

銅張積層板

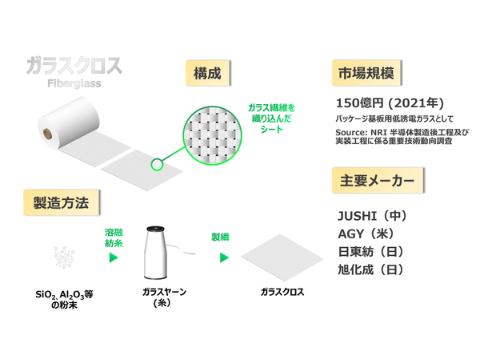

ガラスクロス

半導体技術者1

半導体技術者2

半導体技術者3

半導体技術者4

半導体技術者5

半導体技術者6

指さし呼称

指さし呼称(3人)

エンジニアミーティング

半導体技術者7